“稳定、高效、易用!” 中小学师生对银河麒麟操作系统点赞!

温馨提示:这篇文章已超过488天没有更新,请注意相关的内容是否还可用!

作为麒麟软件的忠实用户和合作伙伴,首都师范大学附属育信学校将从2021年底开始尝试基于国产操作系统的实践教学研究。本学期,中小学三间计算机教室已完成升级改造,改造后,经过老师们的不断实践,已经使用银河麒麟操作系统实现了常规教学!实践证明,采用银河麒麟操作系统的计算机教室与现有硬件设备和软件资源兼容,运行流畅,保证教师和学生正常进行教学。基于银河麒麟操作系统的教学环境充分满足了学生信息技术课程的需求,为推进中小学信息技术机房国产化、落实新课程自主创新教学要求提供了优秀范例标准!

“银河麒麟操作系统完全可以满足我的需求!”

“Linux版本的软件提供了传统软件的替代方案,在稳定性和性能方面表现良好。”

“老师和学生都可以轻松自如地使用它!”

……

这句真挚的话语,来自首都师范大学附属育新学校的师生们。 作为麒麟软件的忠实用户和合作伙伴,首都师范大学附属育信学校将从2021年底开始尝试基于国产操作系统的实践教学研究。本学期,中小学三间计算机教室已完成升级改造,改造后,经过老师们的不断实践,已经使用银河麒麟操作系统实现了常规教学!

实践证明,采用银河麒麟操作系统的计算机教室与现有硬件设备和软件资源兼容,运行流畅,保证教师和学生正常进行教学。 基于银河麒麟操作系统的教学环境充分满足了学生信息技术课程的需求,为推进中小学信息技术机房国产化、落实新课程自主创新教学要求提供了优秀范例标准!

他们说 -

稳定性和性能都非常出色!

“使用银河麒麟操作系统进行信息技术教学半年之后,我发现银河麒麟操作系统完全可以满足我的需求。软件厂商提供了一系列适合教学的Linux版本软件,例如WPS、奇安信可信浏览器等、Mind+等,这些软件可以替代以往教学中使用的Office套件、IE浏览器、Scratch等工具,提供替代传统软件的功能,并且在稳定性和性能方面表现良好。在教学中,我能够高效地开展课程,通过教育让学生感受到我国信息与创新产业的快速发展,培养学生的民族自豪感。”

四年级的学生都非常熟悉了!

“小学四年级的学生已经使用银河麒麟操作系统学习了一个学期的信息技术科目,在这学期的教学中,他们逐渐熟悉了一个新的操作系统。给我印象最深的是银河麒麟。操作系统在广播教学中的应用,四年级学生学习演示时,需要大量的课前演示工作,老师的广播教学使用起来非常流畅,几乎没有延迟和卡顿;基本上每次都幻灯片制作完成后,我会随机选择学生进行视频播放,学生端的直播演示也非常流畅。此外,银河麒麟操作系统的UI设计不仅具有清爽的科技感,而且类似于我们熟悉的WINDOWS系统,所以在系统切换时,老师和学生都可以轻松使用。”

2021年,教育部等六部门印发《关于推进新型教育基础设施建设构建优质教育支撑体系的指导意见》,明确提出“数据中心、信息系统和办公的本地化改造”终端要有序推广,数据中心、信息系统、办公终端国产化要有序推广,使用正版软件。”

麒麟软件不遗余力地推动国产操作系统走进中小学课堂。 麒麟软件已帮助江西、山东、广东、江苏等省市建设基于银河麒麟操作系统的本地化电子教室。 从义务教育阶段开始,普及本土化信息技术基础、办公软件、初级编程等课程,逐步增强中小学生对国产软件的了解,培养自主创新意识。 让中小学生学好用好国产软件,激发学生使用“中国魂”的兴趣和创新热情。

正如首都师范大学附属育新学校所言,基于国产操作系统的教学实践是必要的、可行的。 随着技术的发展和政策的支持,国产操作系统及相关应用将在教育领域得到更广泛的推广和应用,为提高信息化水平和教学质量做出重要贡献。 “不忘初心、铸就匠心、育新人”,麒麟软件将积极推动教育创新人才培养和教育行业数字化转型,让科技教育成为学生成长的“催化剂”。成长,用中国科技创造中国智慧!

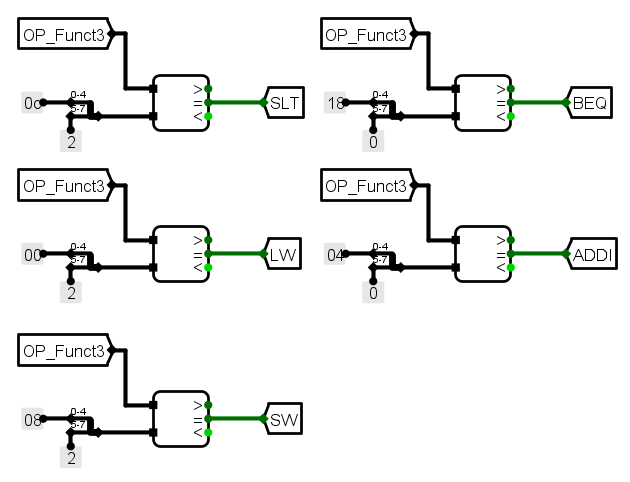

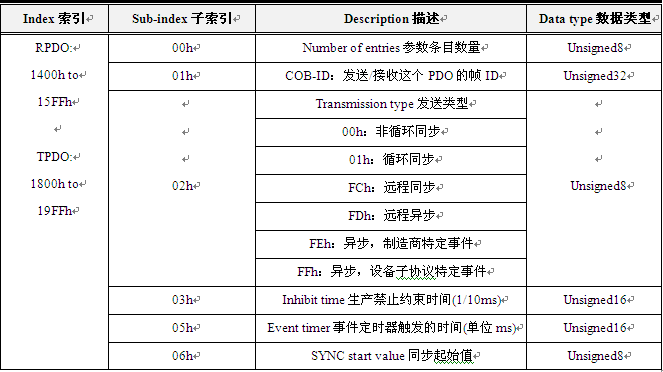

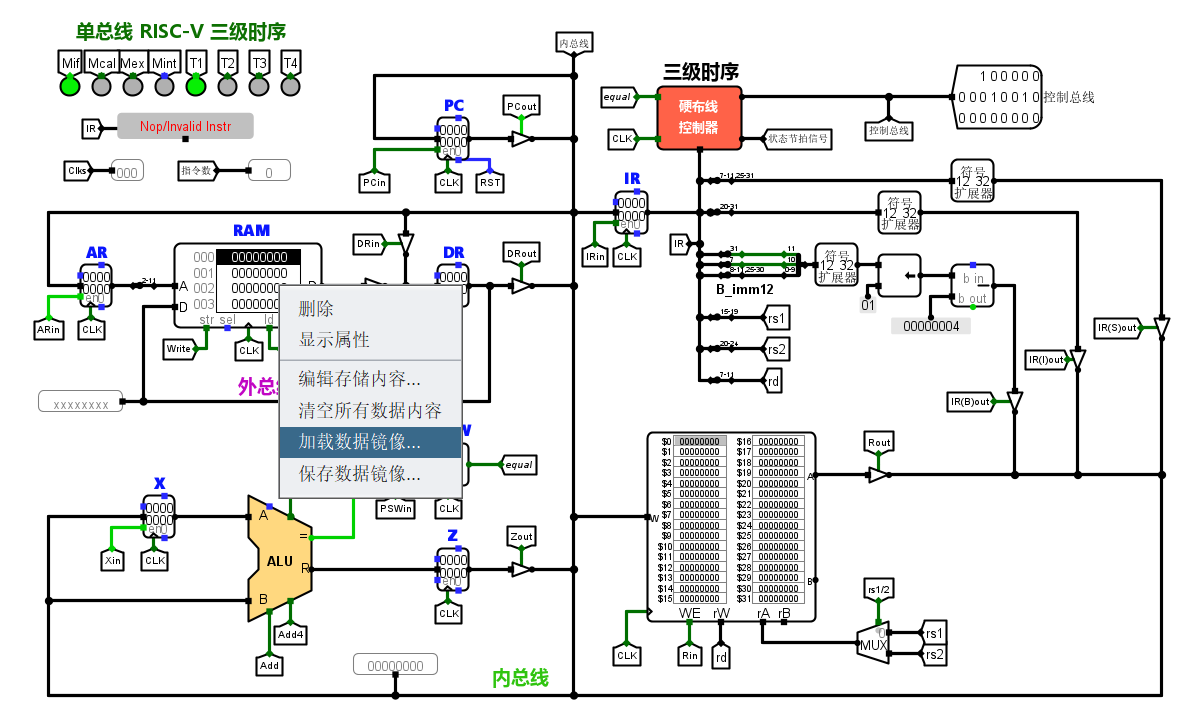

HUST组原创实验单总线CPU设计(三级时序)1.RISC-V指令译码器设计

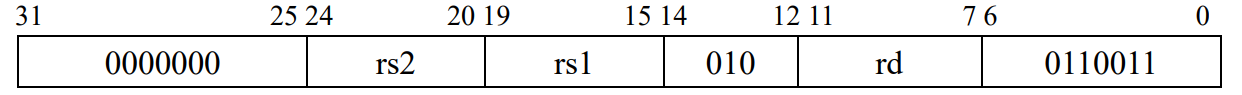

查阅RISC-V指令手册并使用Ctrl+F搜索这些指令,或者查阅大罗博发布的RISCV指令代码表,可以得到以下指令代码。

命令OPCODEFUNCT3

长波

00000 11

010

SW

01000 11

010

均衡器

11000 11

000

阿迪迪

00100 11

000

斯莱特

01100 11

010

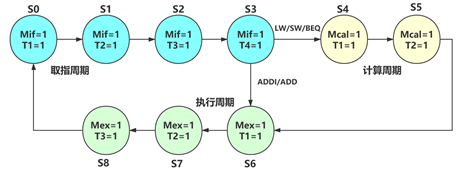

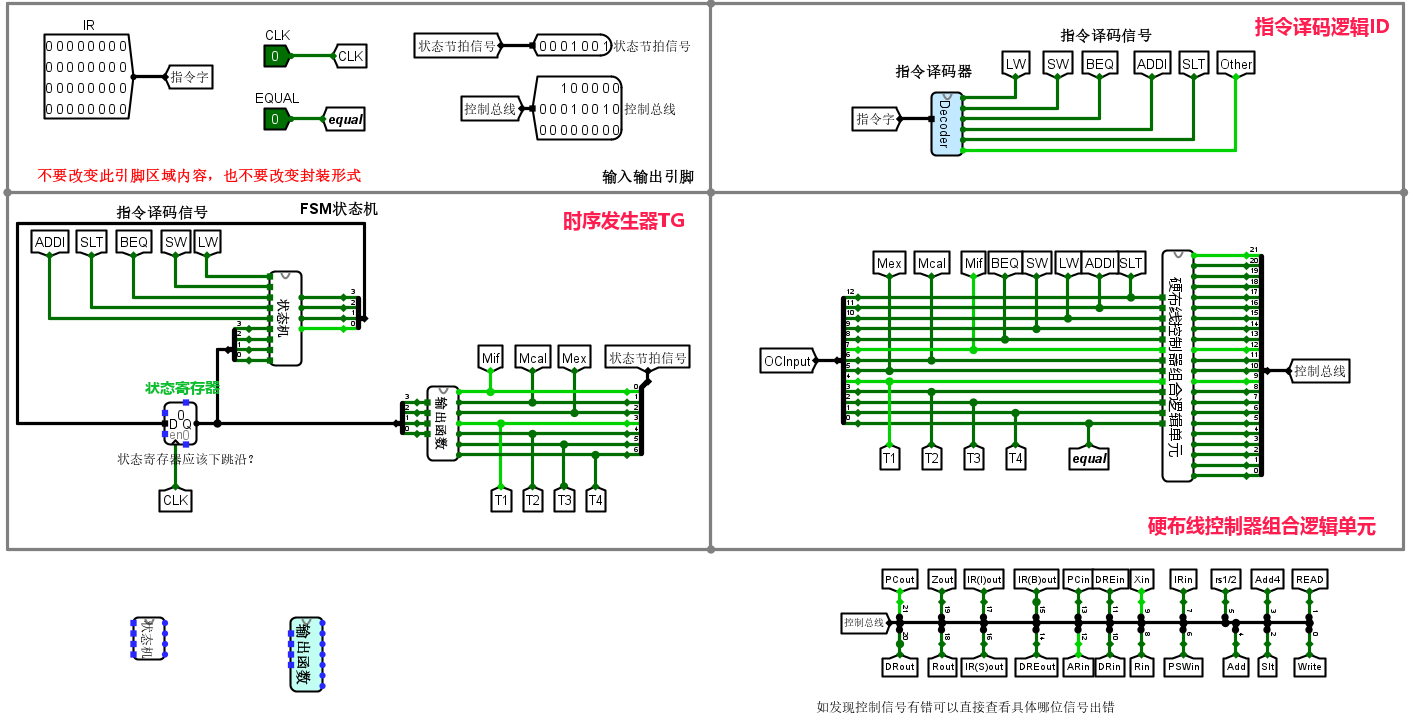

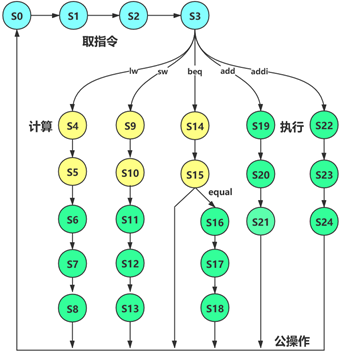

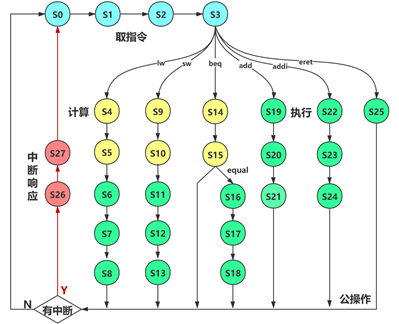

2、变长指令周期——定时发生器FSM设计

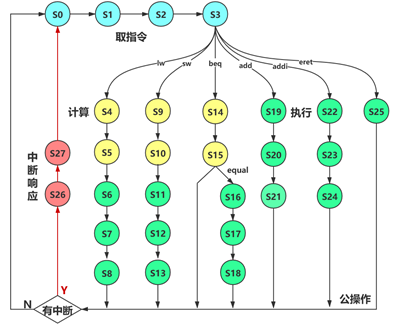

如果在单总线结构中采用变长指令周期,则不同指令的机器周期数不同,每个机器周期的节拍数也是可变的。 具体状态图如下:

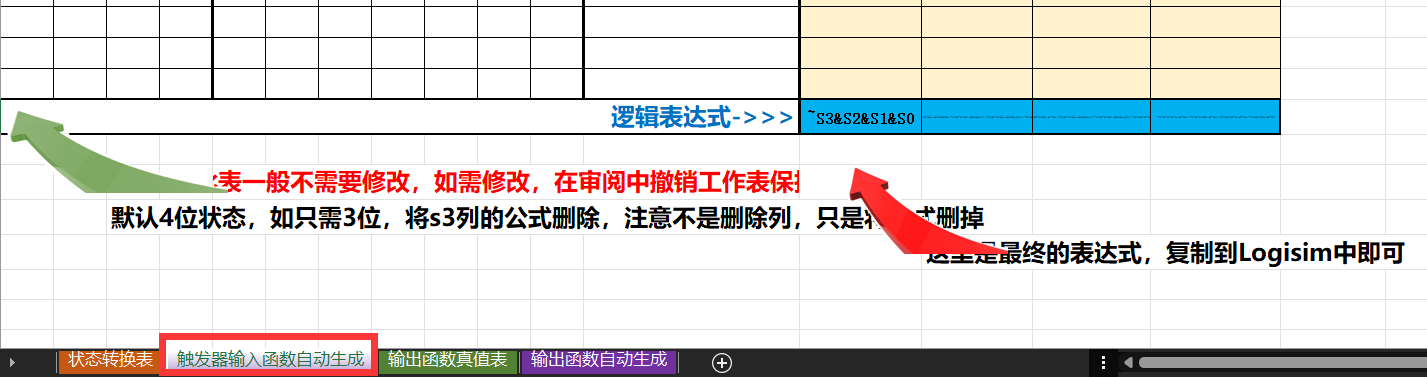

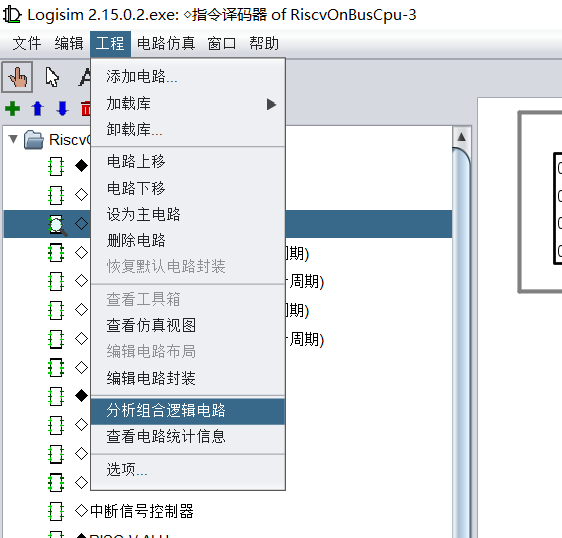

打开项目->分析组合逻辑电路。

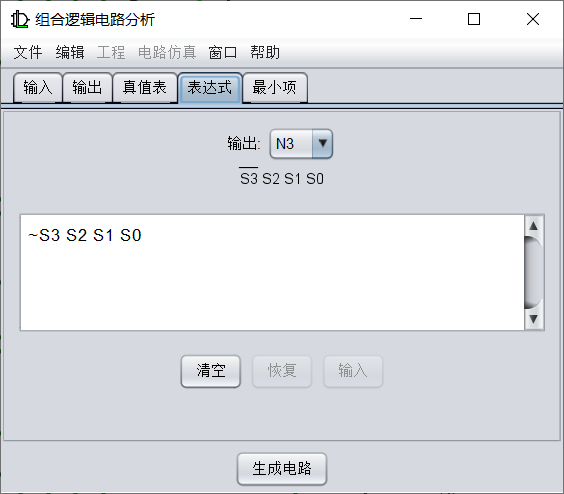

将相应的表达式复制到相应的输出。

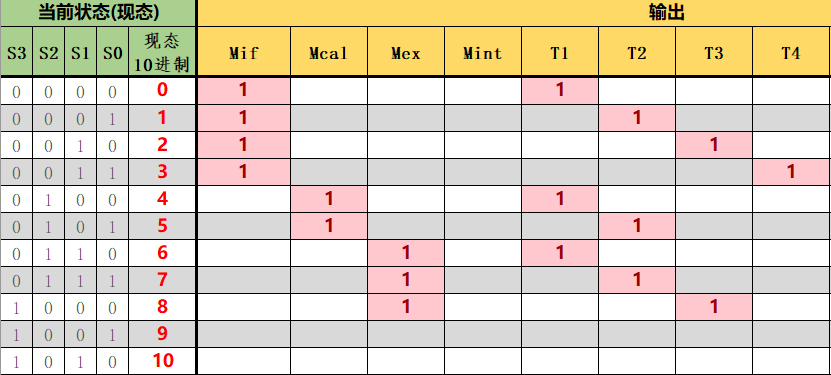

3、变长指令周期——时序发生器输出函数设计

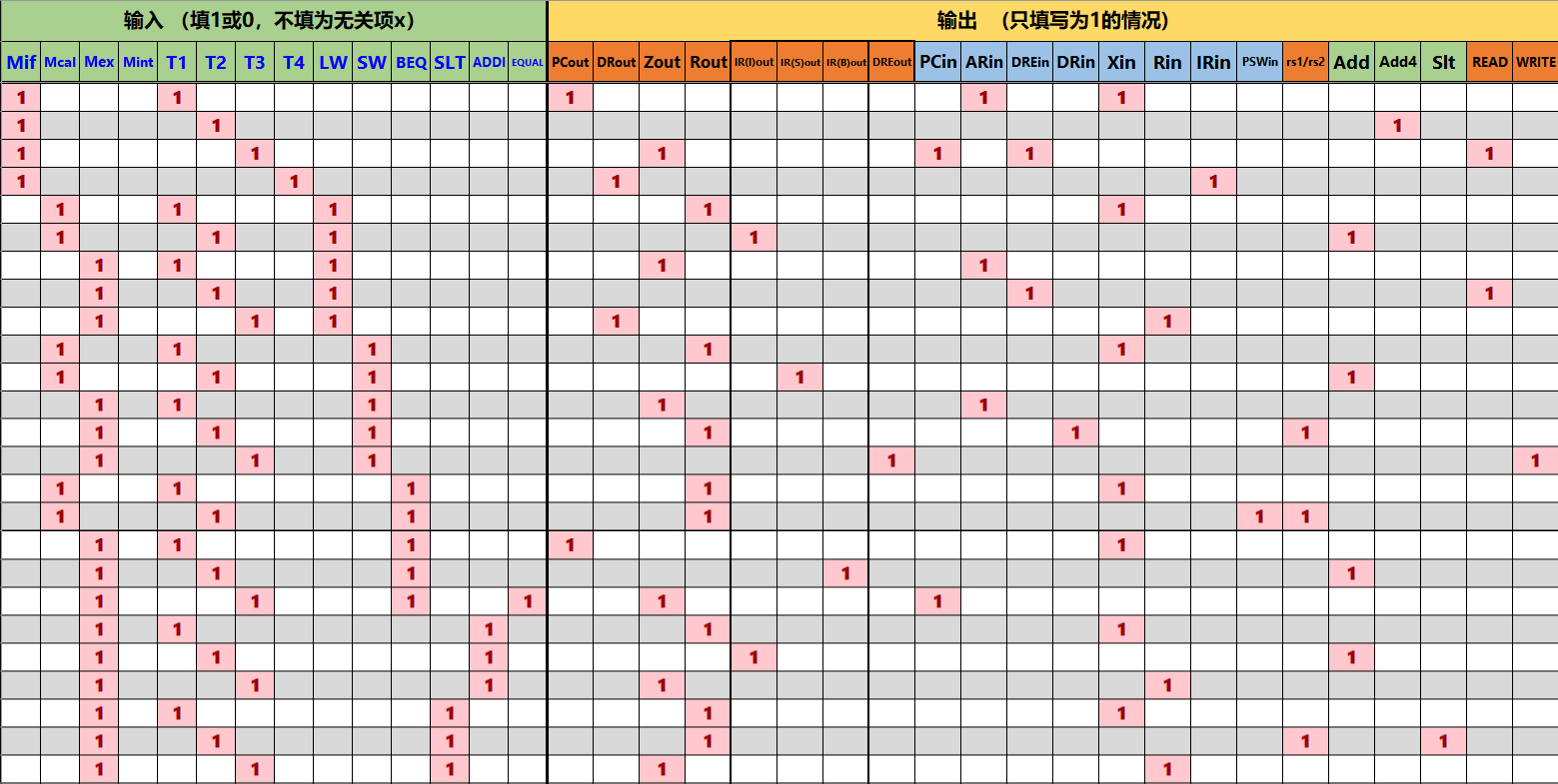

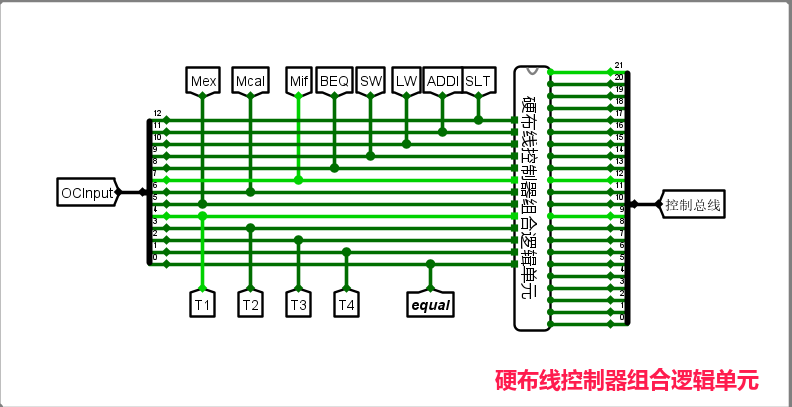

4. 硬连线控制器组合逻辑单元

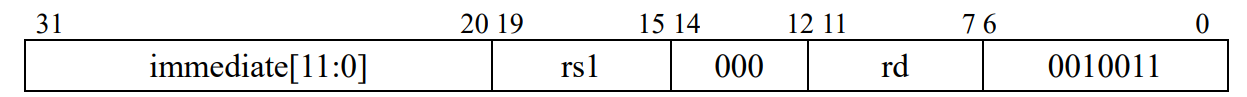

此级别需要全面的指令周期、节拍和控制信号填入表格。 详细内容需要参考最新的第6章RISCV典型5指令操作流程以及大罗博发送的控制信号(第P13页)。

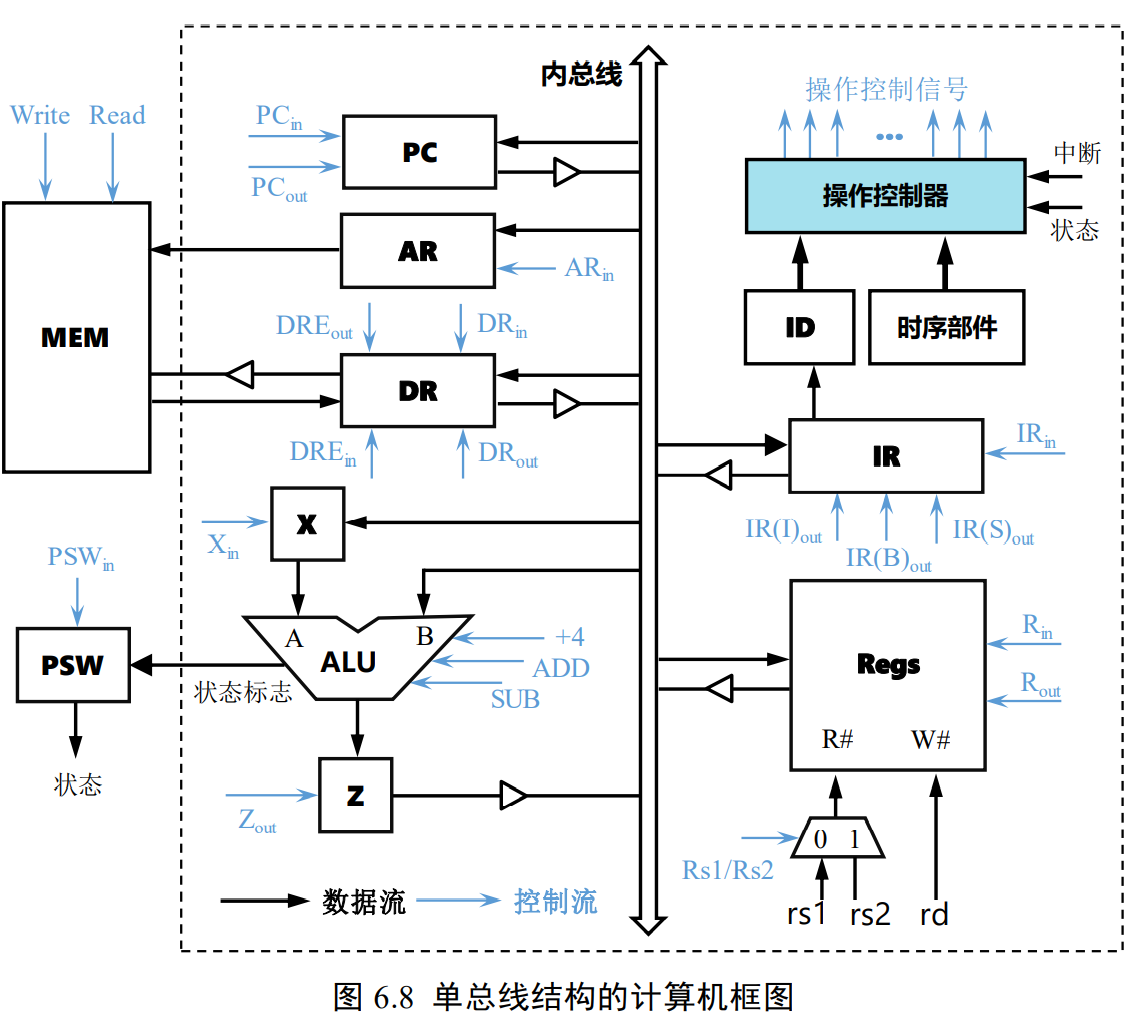

首先,熟悉一下单总线CPU的结构。

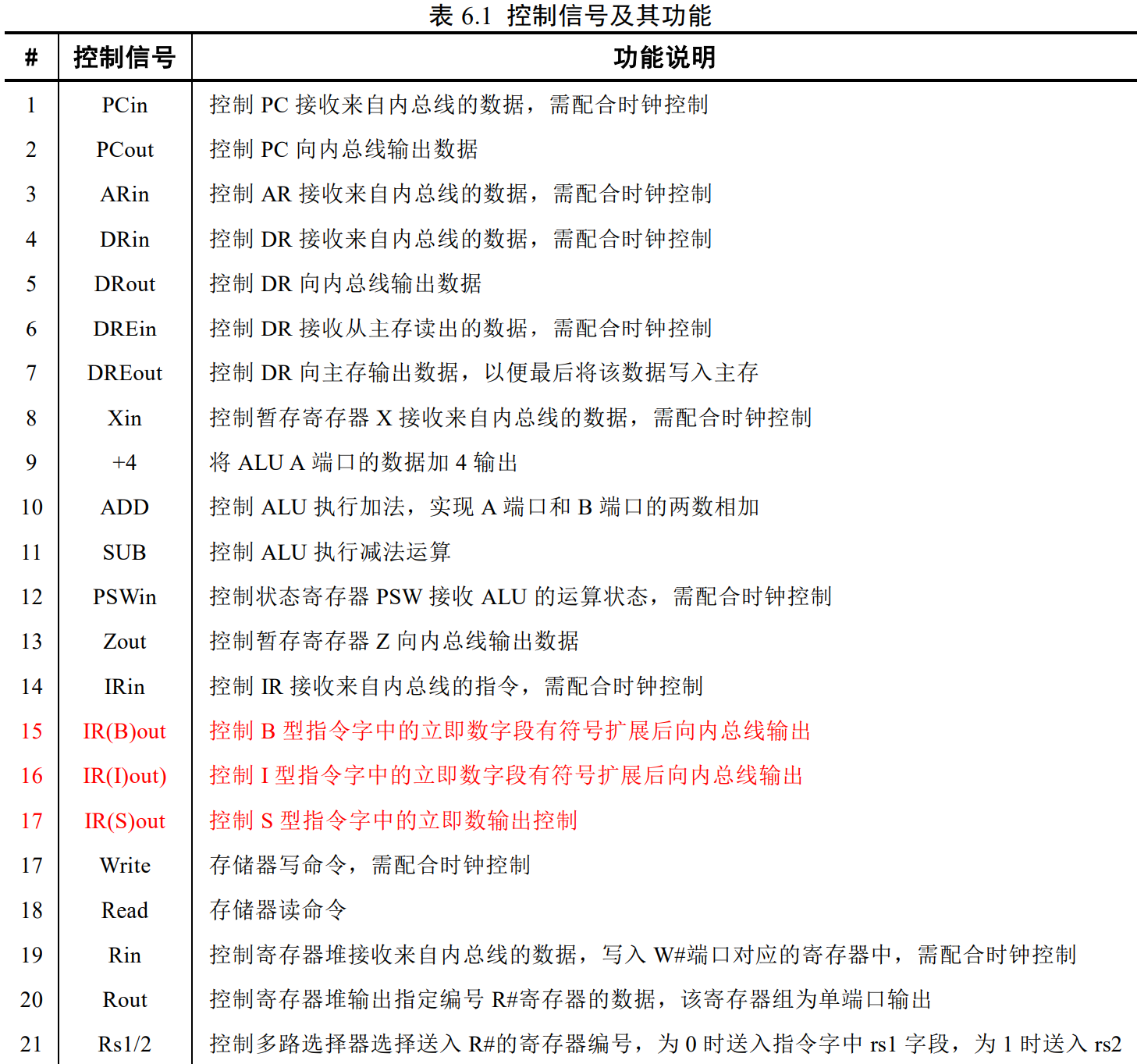

以下为控制信号及功能,方便参考。

指令对应的结构和功能

x代表寄存器,x[rs1]是寄存器号rs1。

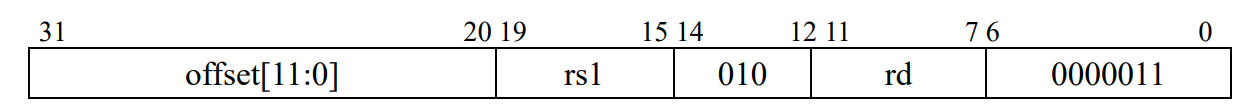

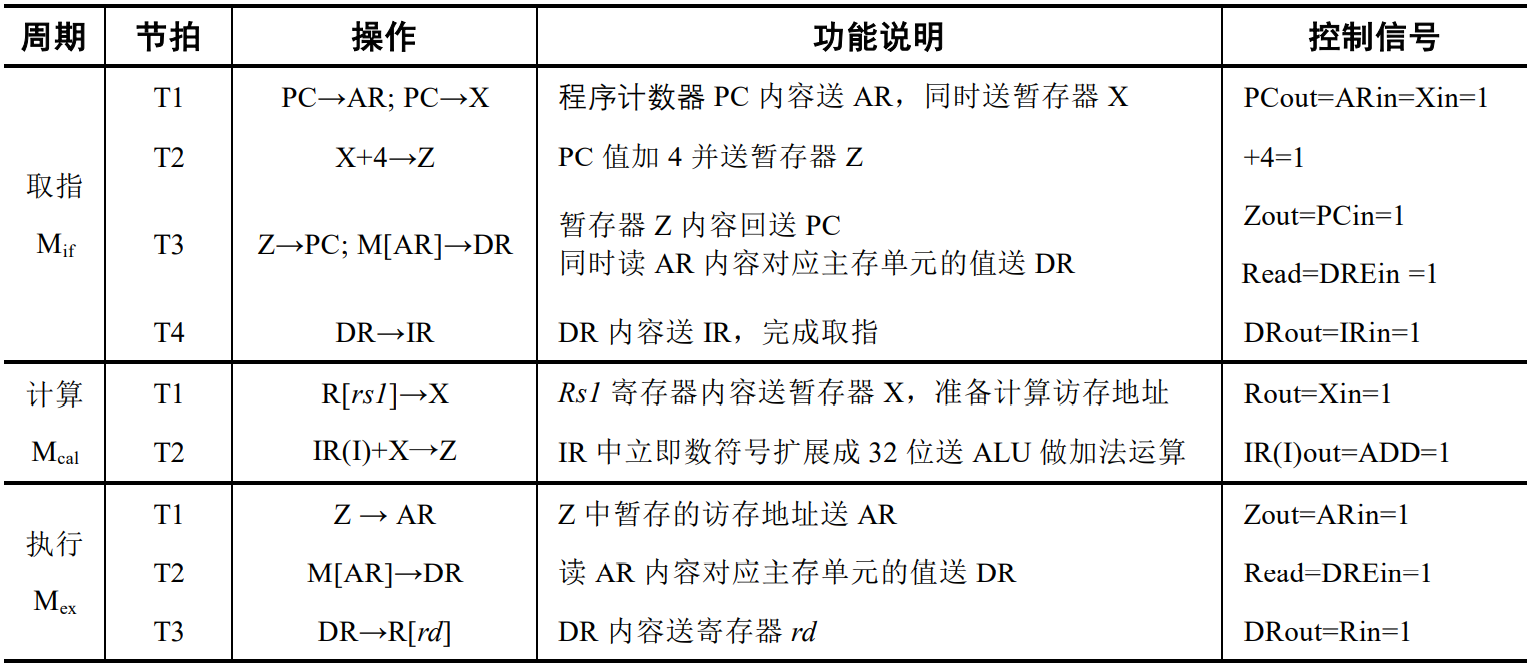

LW:从主存地址x[rs1]+sign-extend(offset)读取四个字节并写入x[rd]。 12 位立即偏移符号扩展为 32 位,然后才能发送到 ALU 计算内存访问地址。 是 典型的索引寻址。

汇编代码为lw rd,offset(rs1)

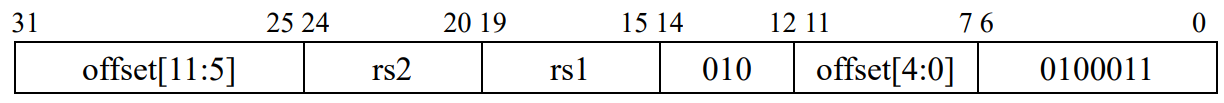

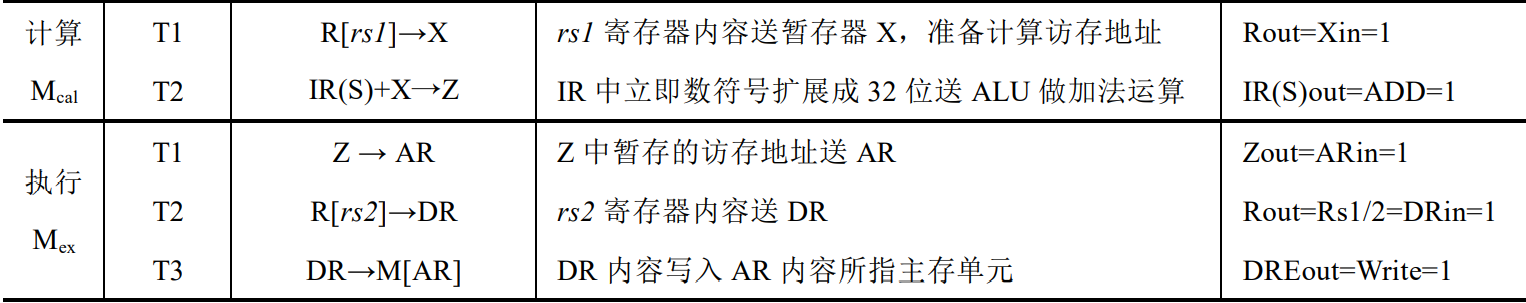

SW:将x[rs2]的4个字节存储到主存地址x[rs1]+sign-extend(offset)中。

汇编代码为 sw rs2,offset(rs1)

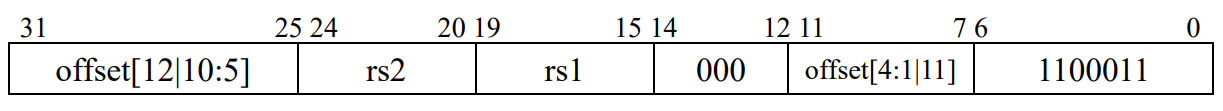

BEQ:如果寄存器x[rs1]和寄存器x[rs2]的值相等,则将PC的值设置为当前值加上符号位扩展的偏移量offset。

汇编代码为beq rs1, rs2, offset

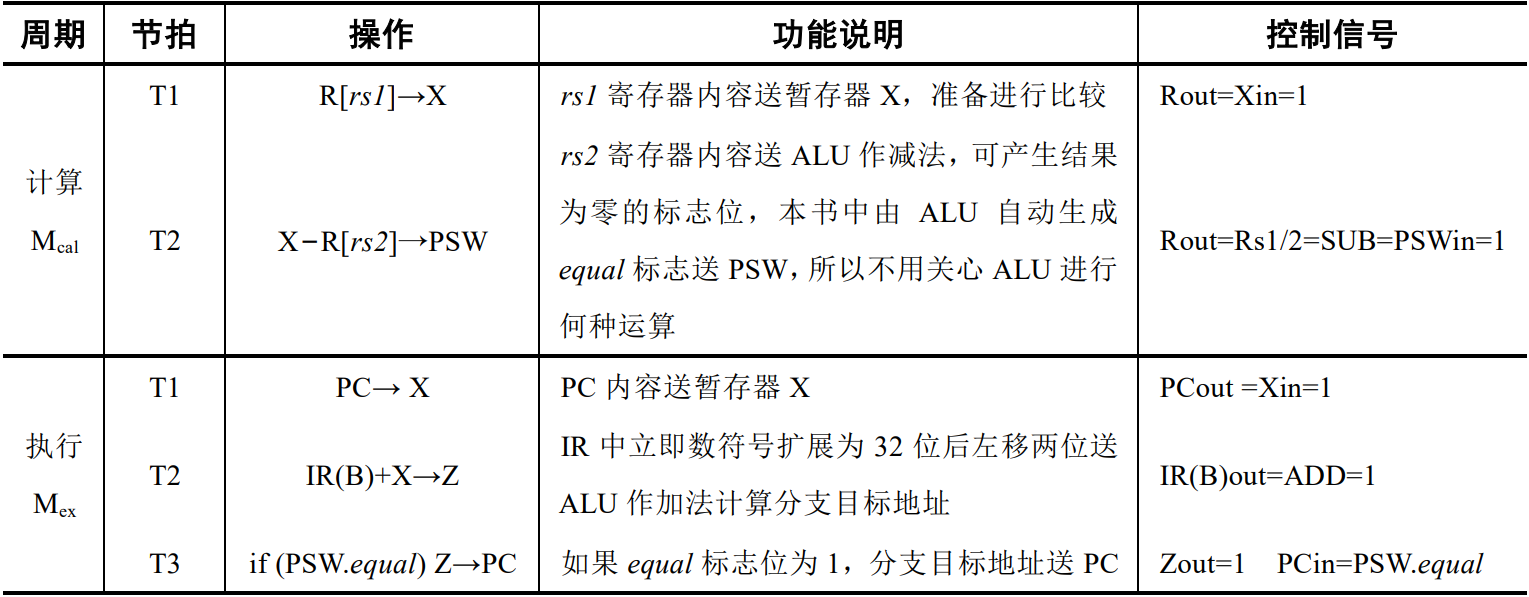

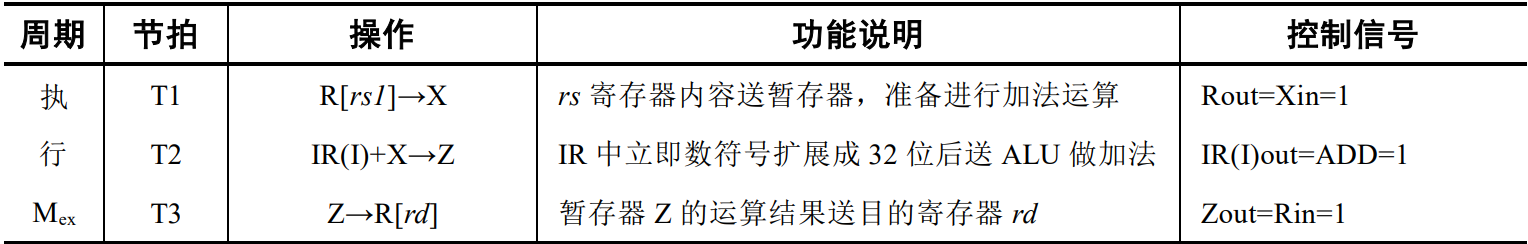

ADDI:将符号扩展立即数与寄存器x[rs1]相加,并将结果写入x[rd]。 算术溢出将被忽略。

汇编代码为addi rd, rs1, imm

SLT:比较 x[rs1] 和 x[rs2] 中的数字。 如果x[rs1]较小,则将1写入x[rd],否则写入0。

汇编代码为 slt rd, rs1, rs2

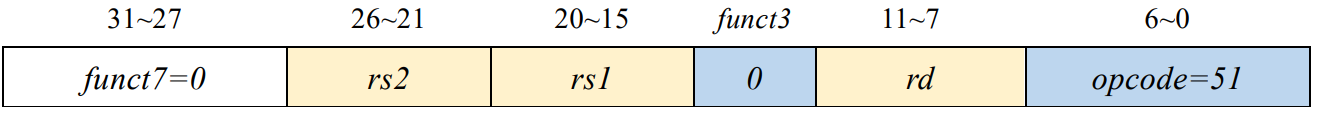

ADD:将rs1和rs2寄存器的相加结果发送到rd寄存器。

汇编代码为add rd, rs1, rs2

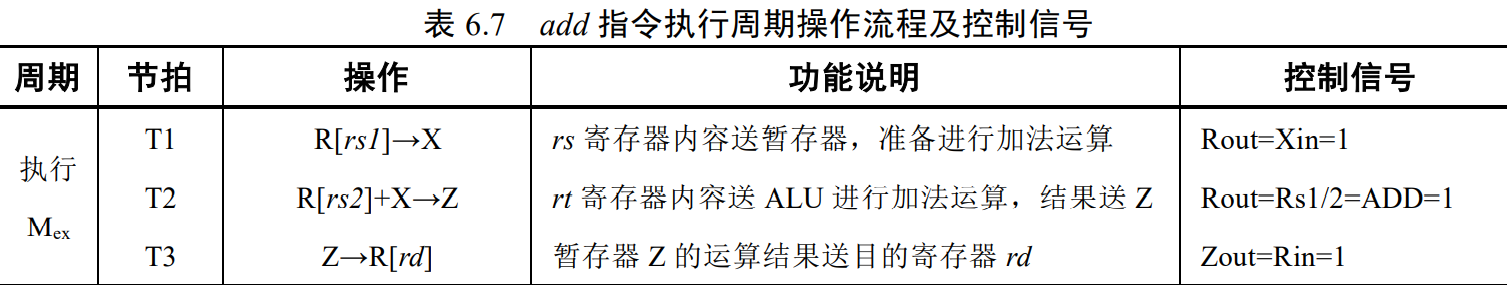

由此可推导出SLT的控制信号:

节拍操作 功能说明 控制信号

T1

R[rs1]→X

rs1寄存器的内容被发送到临时寄存器X,准备进行操作。

路由=辛=1

T2

R[rs2]+X→Z

将rs2寄存器的内容送入ALU进行SLT运算,结果送至Z

路由=Rs1/2=SLT=1

T3

PSW→R[rd]

临时寄存器Z的运算结果被发送到目的寄存器rd。

佐特=凛=1

可见,与ADD指令相比,SLT指令只是将T2节拍的ADD信号改为SLT信号来控制ALU操作。

至此,所有周期性节拍对应的信号已经确定。 填写表格后,表达式可以输入到logisim生成电路中。

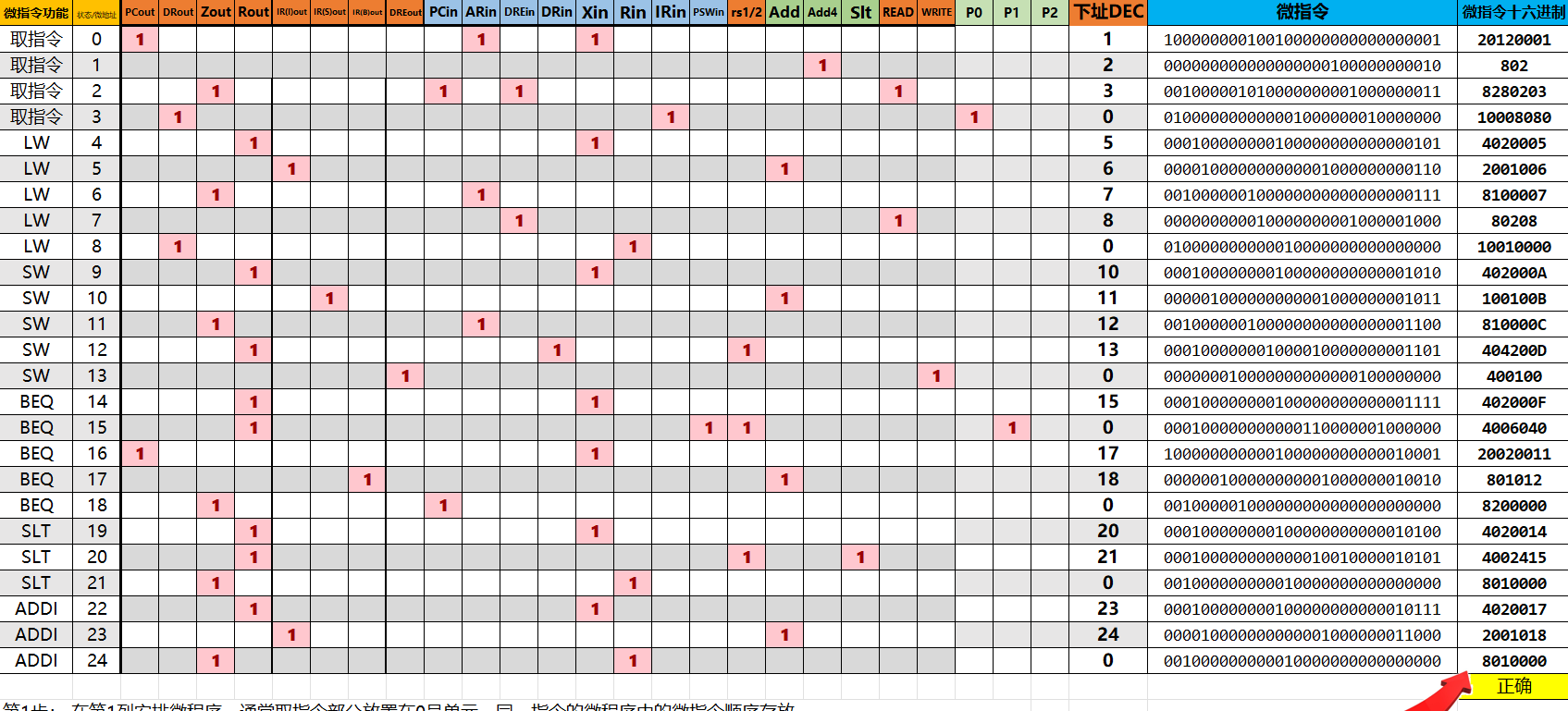

表格如下:

调试

如图所示,控制总线信号有错误。 ErrBit指出错误信号的第1位,0d指出错误发生在第12位。 这时,首先应该检查硬连线控制器中的组合逻辑单元。 这时,可以根据OCinput,判断哪条指令、哪一个周期、哪一个节拍有问题(图中0284(00010 100 0010 0)代表:SW指令、Mif周期、T3节拍),然后找到根据发生问题的线路的错误信号,将其更改为ControlBus的正确信号。

5. 可变长度指令周期——硬连线控制器设计

6. 变长指令周期——单总线CPU设计

单总线CPU设计(现代时序)一、RISC-V单总线CPU设计

与上面相同

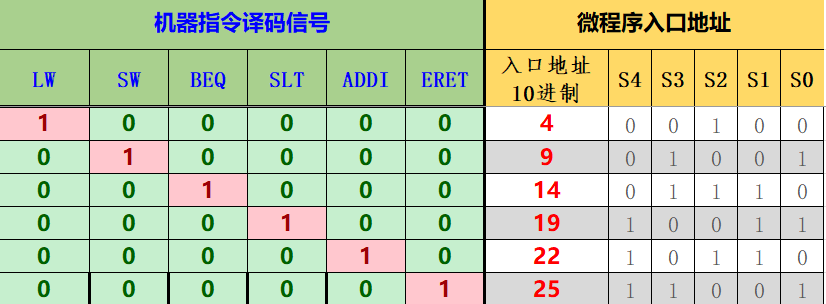

2、单总线CPU微程序入口查找逻辑

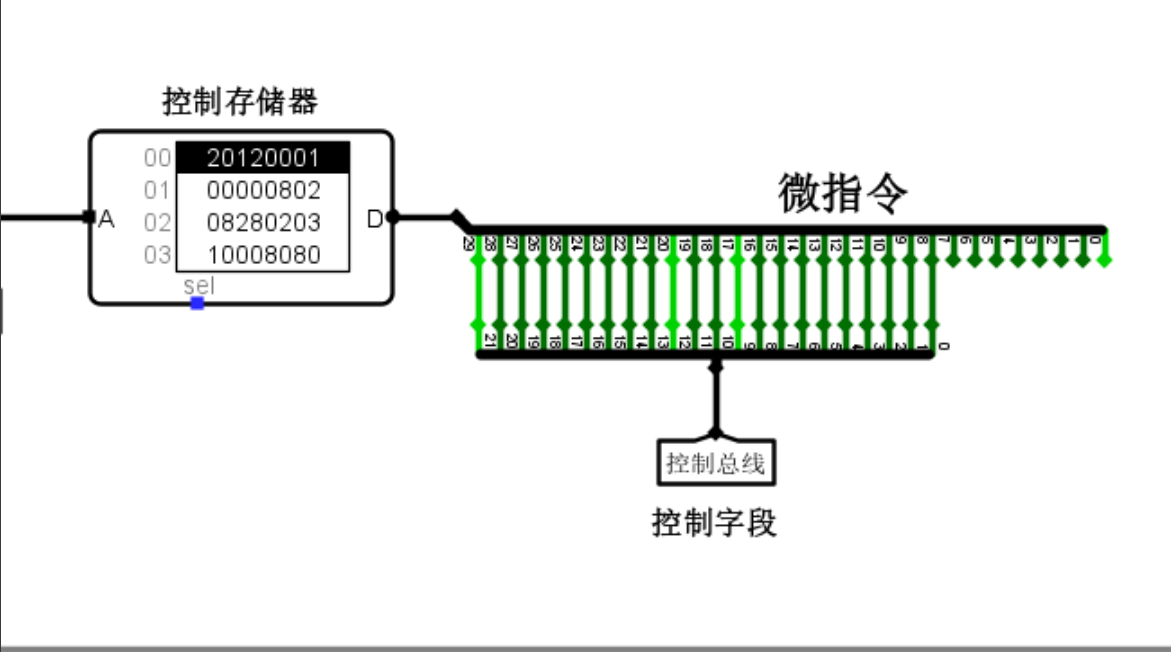

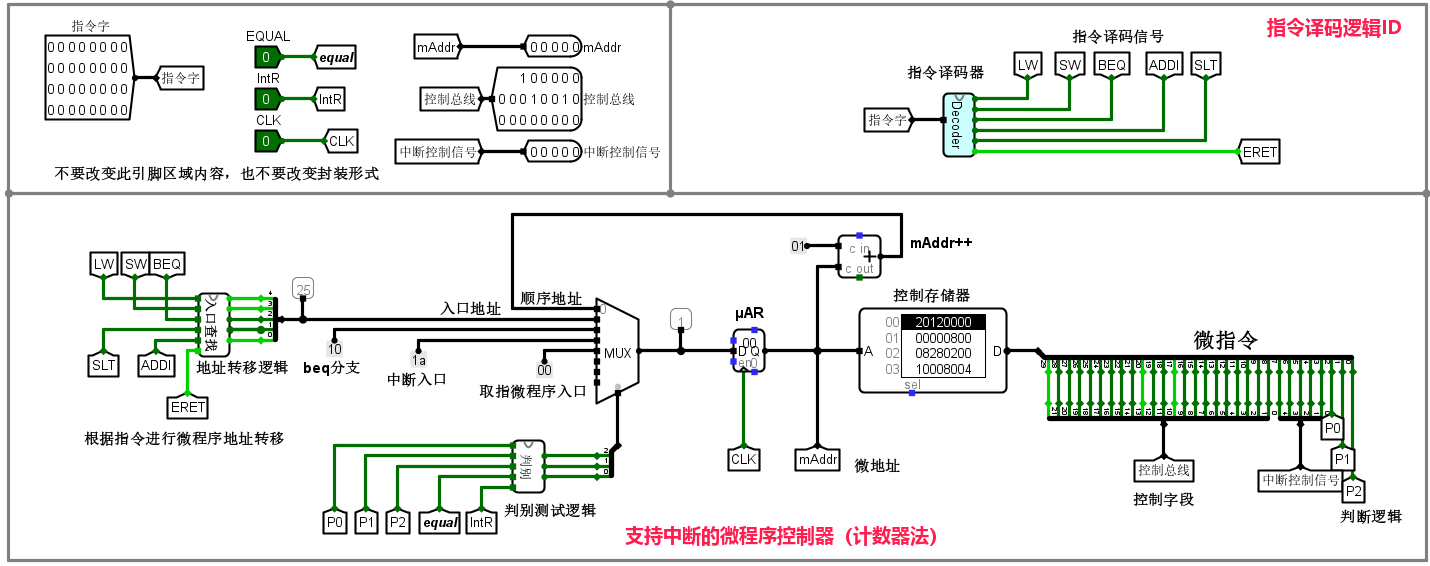

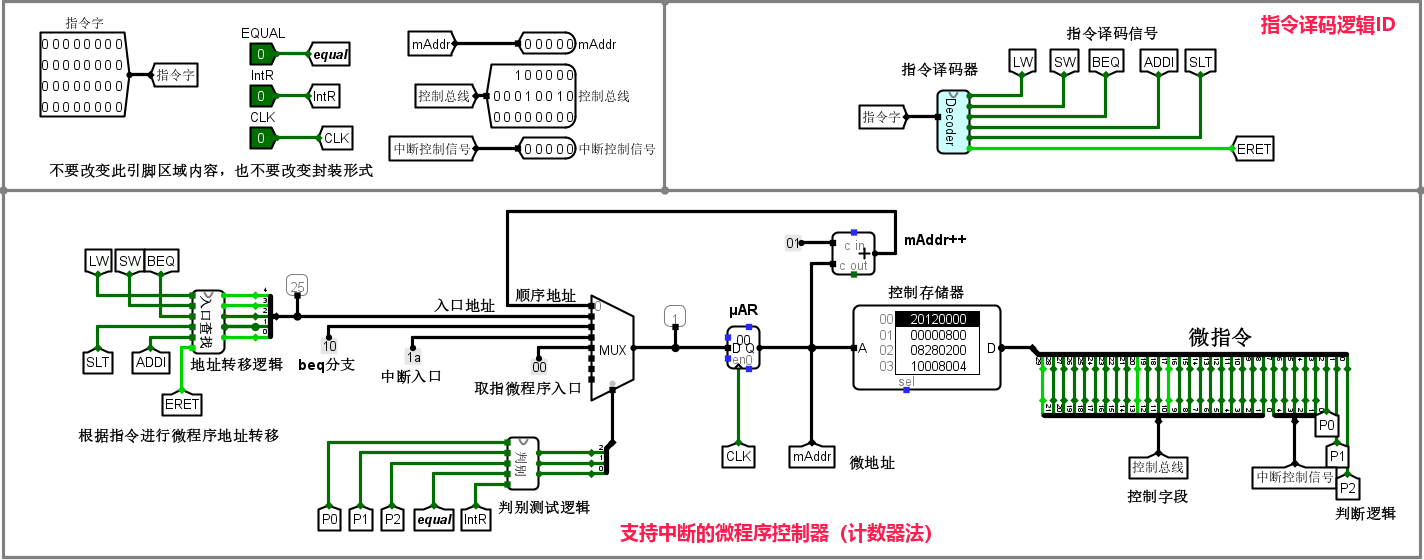

微程序:遵循编程的基本方法,将指令系统中实现全部指令功能所需的所有控制信号按照一定的规则编码成微指令。 实现同一指令功能的若干条微指令就构成了一个微程序。

实现所有指令的微程序存储在只读存储器中,称为控制存储器。

每条机器指令对应一个微程序,一个微程序又包含若干条微指令。

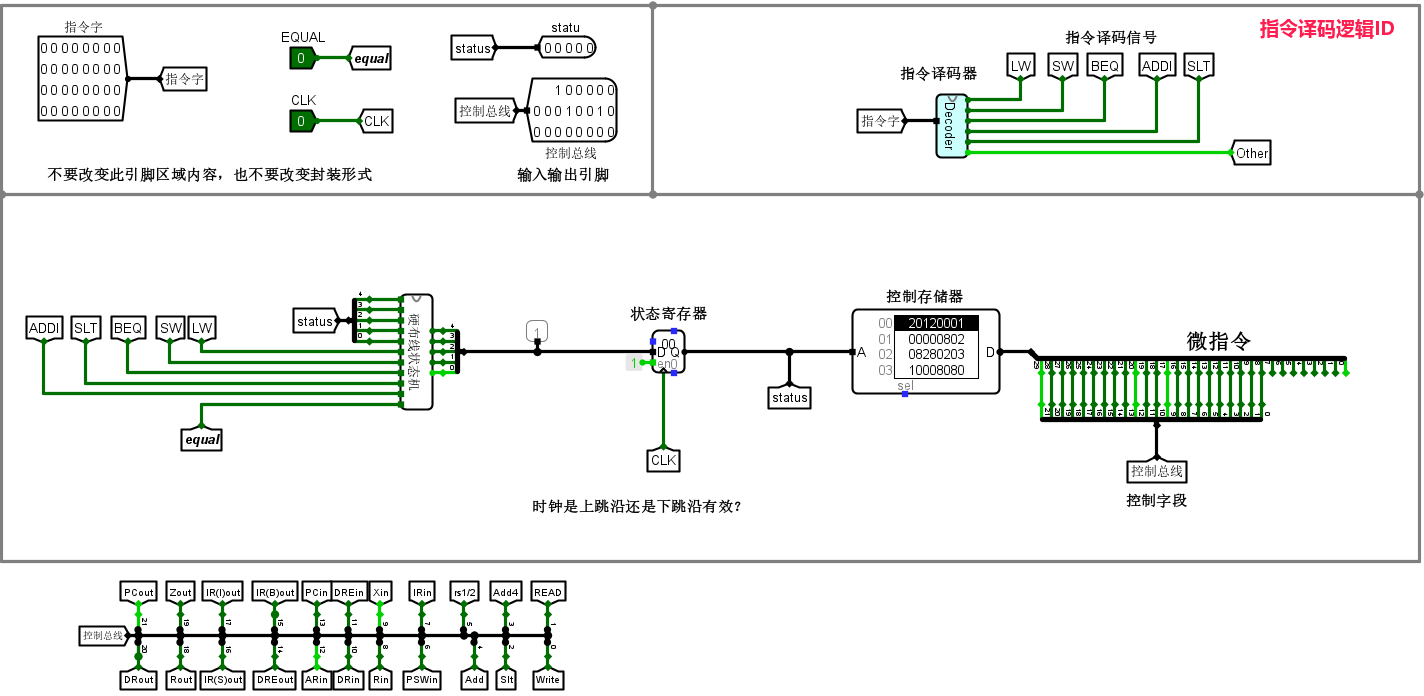

最后一个实验是用电路实现控制信号,还是那张图。

本实验中使用的微程序将所有控制信号放入控制存储器中。

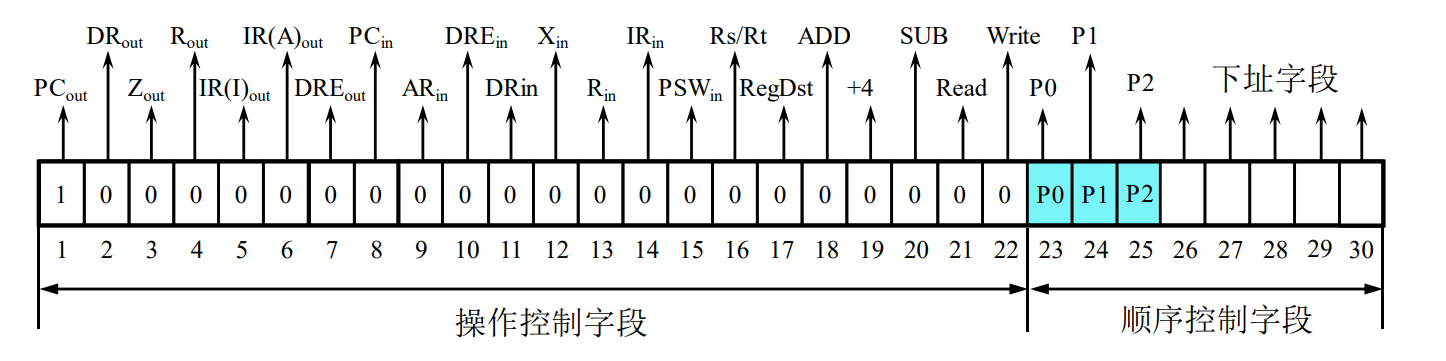

从控制存储器中取出的数据,即微指令字,包括三部分:微操作控制字段、判别测试字段、低地址字段。 低位地址字段用于指示下一个要访问的微指令的地址,鉴别字段用于地址逻辑。 转移。

本实验采用低地址域方式,低地址域直接给出下一条微指令的地址。 下面的状态机用于设计微指令的存储。

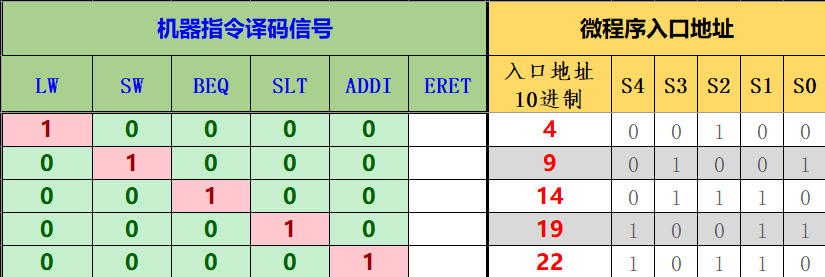

因此,这5条指令的入口地址是按顺序确定的。

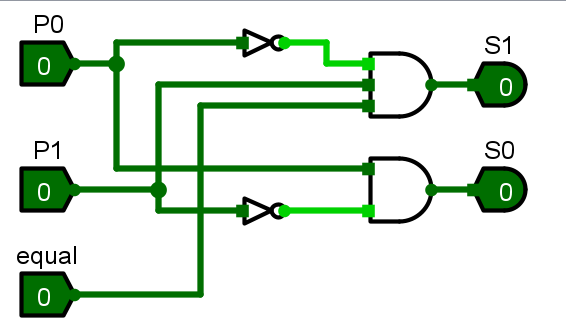

只需从逻辑表达式生成电路即可。

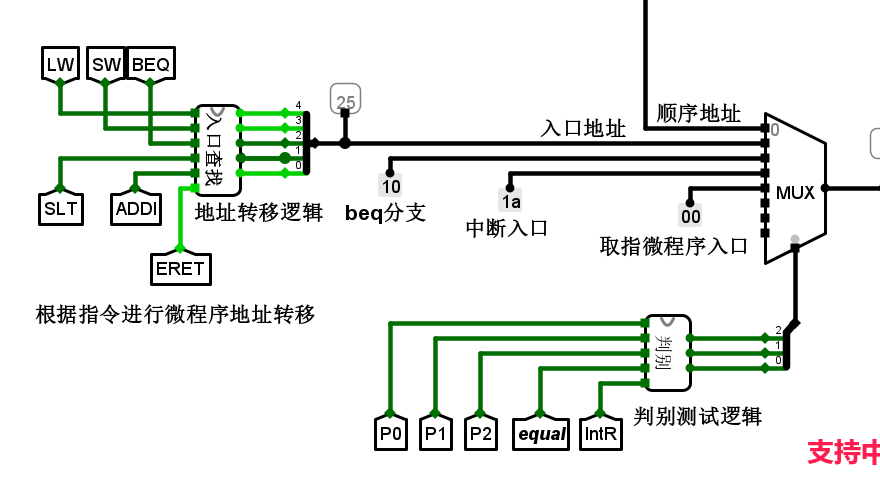

3、单总线CPU微程序条件判断测试逻辑

判别测试字段(上图中控制信号中的P0-P2)指出了微指令执行过程中需要测试的外部条件,如是否根据指令译码进行微程序分支、进位、是否运算结果是否为零、是否是当前微程序、最后一条微指令等。

信号输入输出位宽功能说明

P0

进入

判别测试位,如果为1,则表示微程序应按照指令功能进行分支。

P1

进入

判别测试位,如果为1,则表示微程序应根据相等标志进行分支。

平等的

进入

条件状态位,表示操作是相等的

S4~S0

进入

当前输出位0

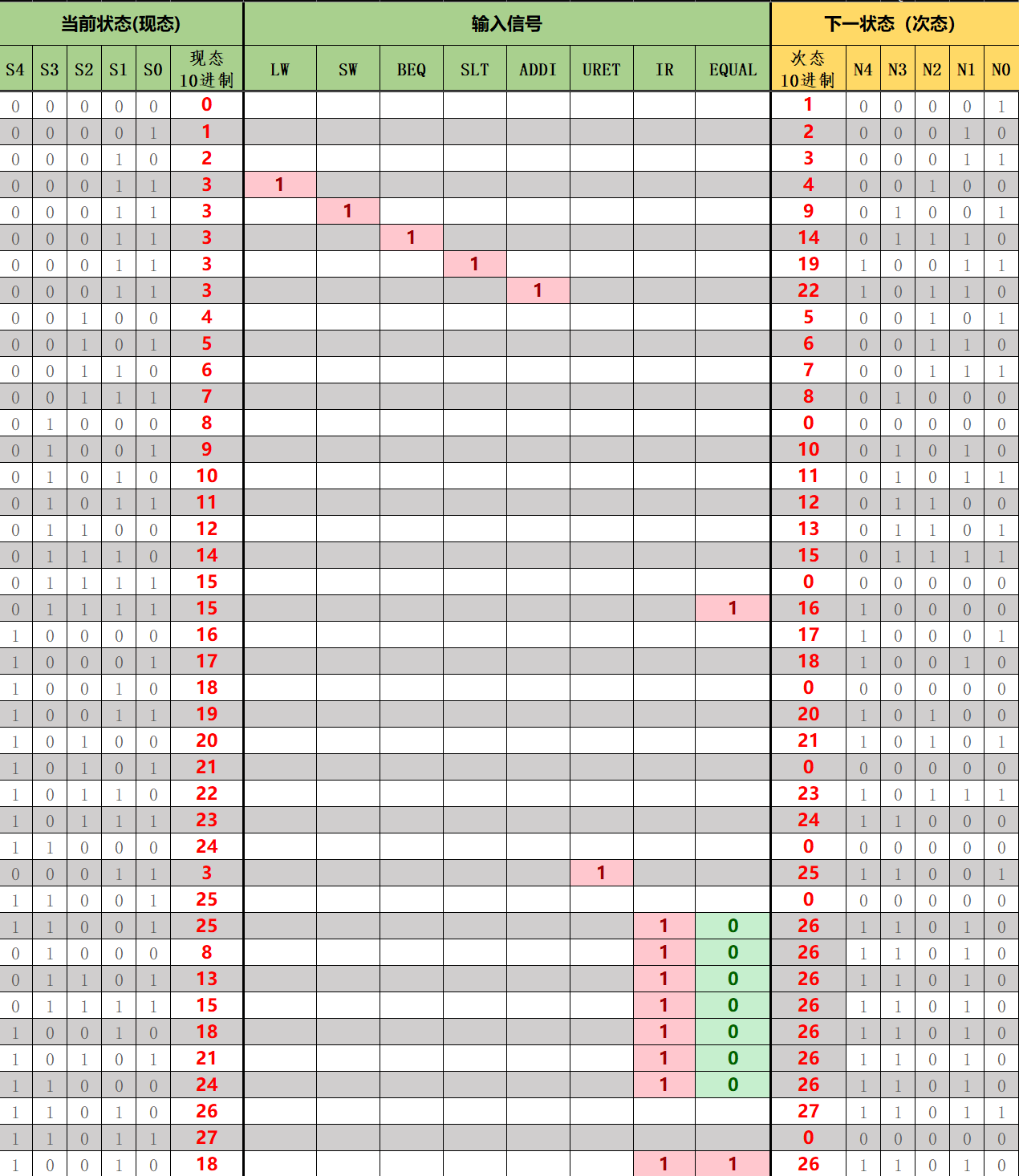

根据信号填表即可(因为后续的中断实验会用到该表,所以本次实验已覆盖)。 最终电路如下。

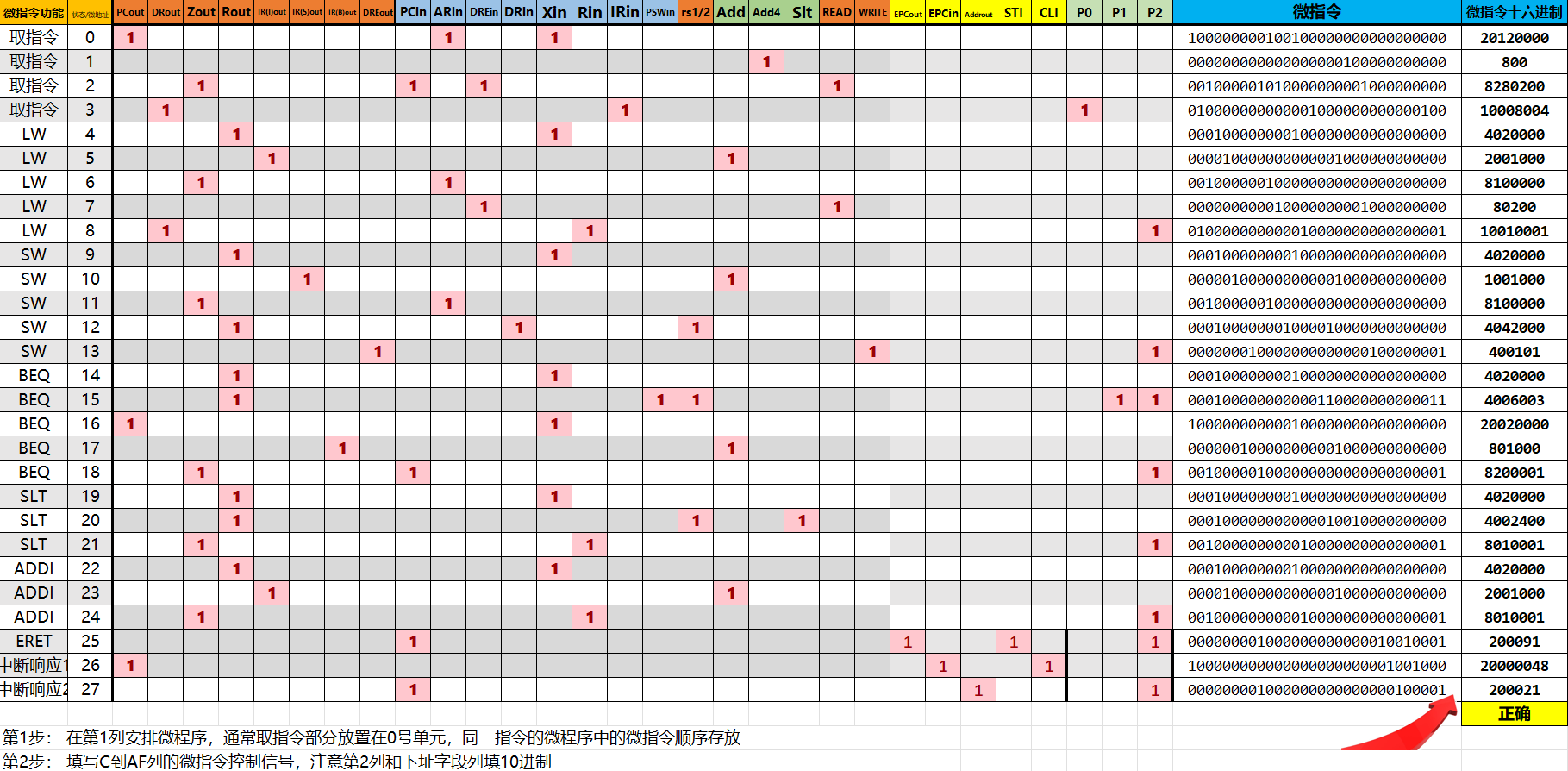

4、单总线CPU微程序控制器设计

只需将三电平时序实验的控制信号填入下表即可。 较低的地址字段是微指令地址+1。注意beq 分支。

填写完毕后,右下角的检查框就会显示正确。

5. 使用微程序的单总线CPU设计

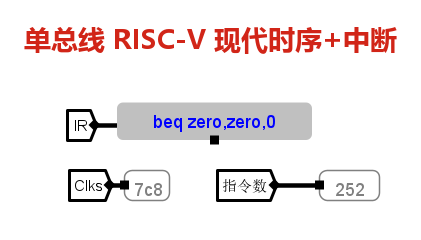

将 sort-5-riscv.hex 程序加载到 RAM 中并自动运行 ctrl+k。 程序应该运行到 0x7c1 节拍并停止。 指令数为251。注意最后一条指令是beq分支指令,会跳回当前指令继续执行。 ,是一个无限循环。

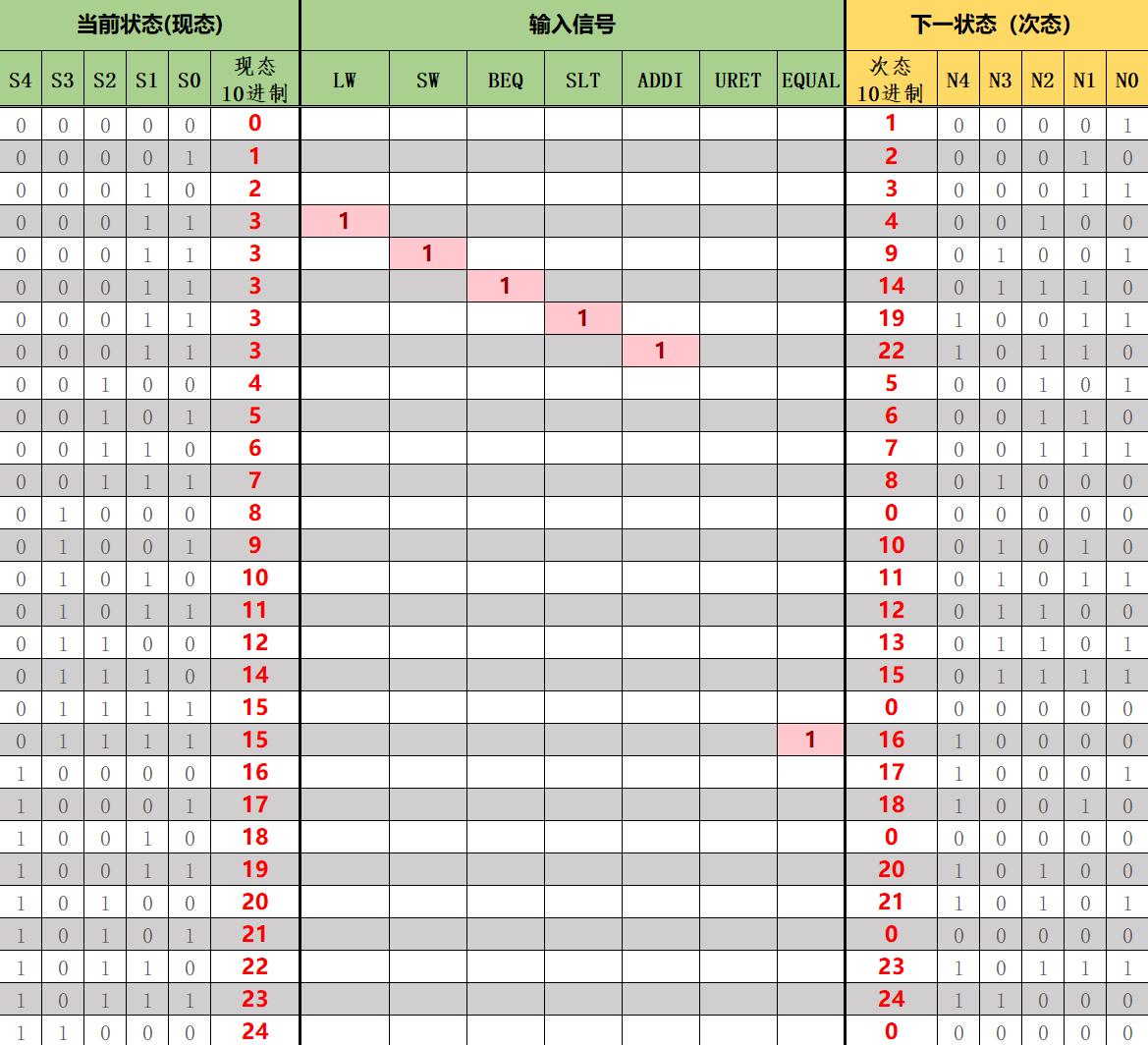

6. 现代顺序硬连线控制器状态机设计

还是根据这个状态转换图来填写表格。

7. 现代顺序硬连线控制器设计

只需正确连接即可。

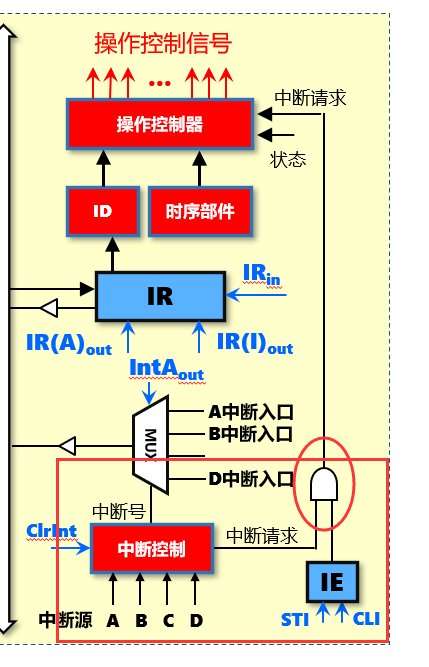

RISC-V现代时序中断机制实现2.支持中断的微程序入口搜索逻辑

与之前的实验相比,只多了一条中断指令。

只需根据这个添加中断的状态转换图填写表格即可。

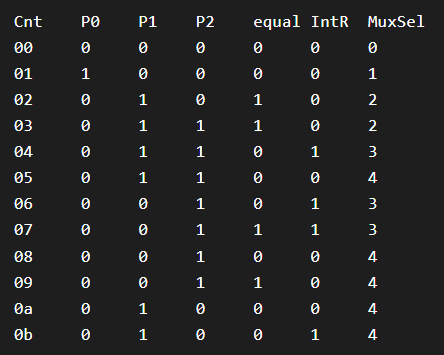

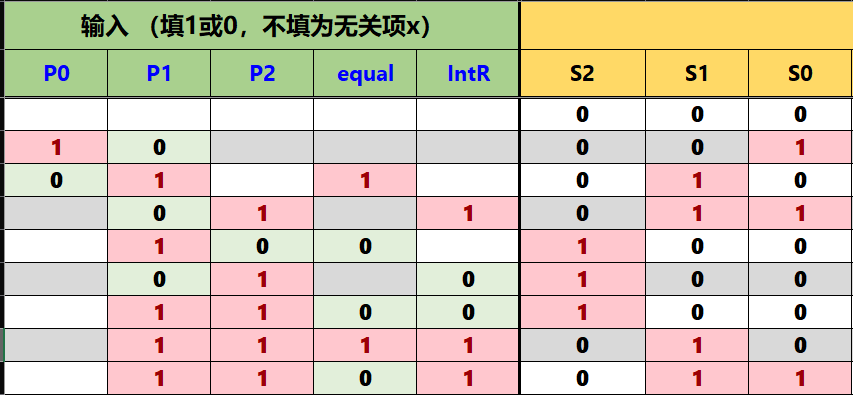

3、支持中断的微程序条件判断测试逻辑

信号功能说明

碳数

测试用例编号,注意是十六进制

P0

条件测试位,根据指令功能执行微程序分支P~IR~

P1

条件测试位,根据 PSW.equal mark 分支 Peequ

P2

条件测试位,表明是最后一条微指令,需要判断中断请求IntR

平等的

平等标记

tR

中断请求信号

复用器选择

后续地址复用控制信号

由于在后续实验中发现该表格不正确,因此为实验测试集编写的表格仅供参考。

4、支持中断的微程序控制器设计

只需正确连接即可。

5、支持中断的微程序单总线CPU设计

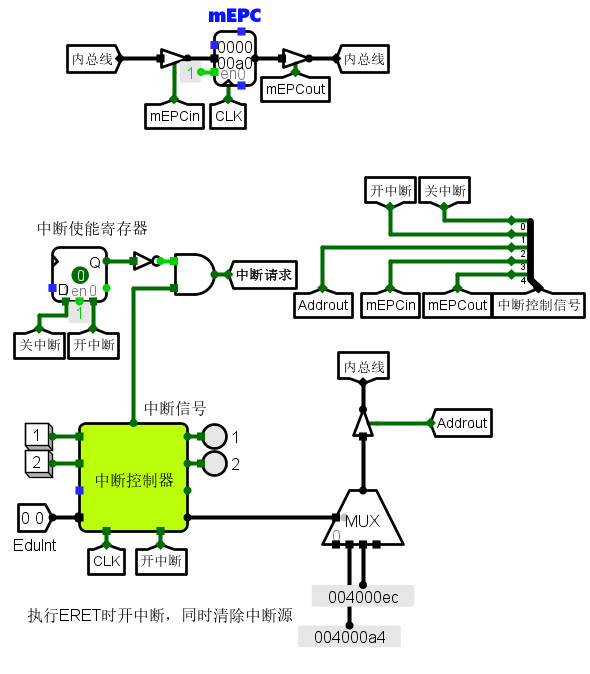

按照中断控制器原理图接线。

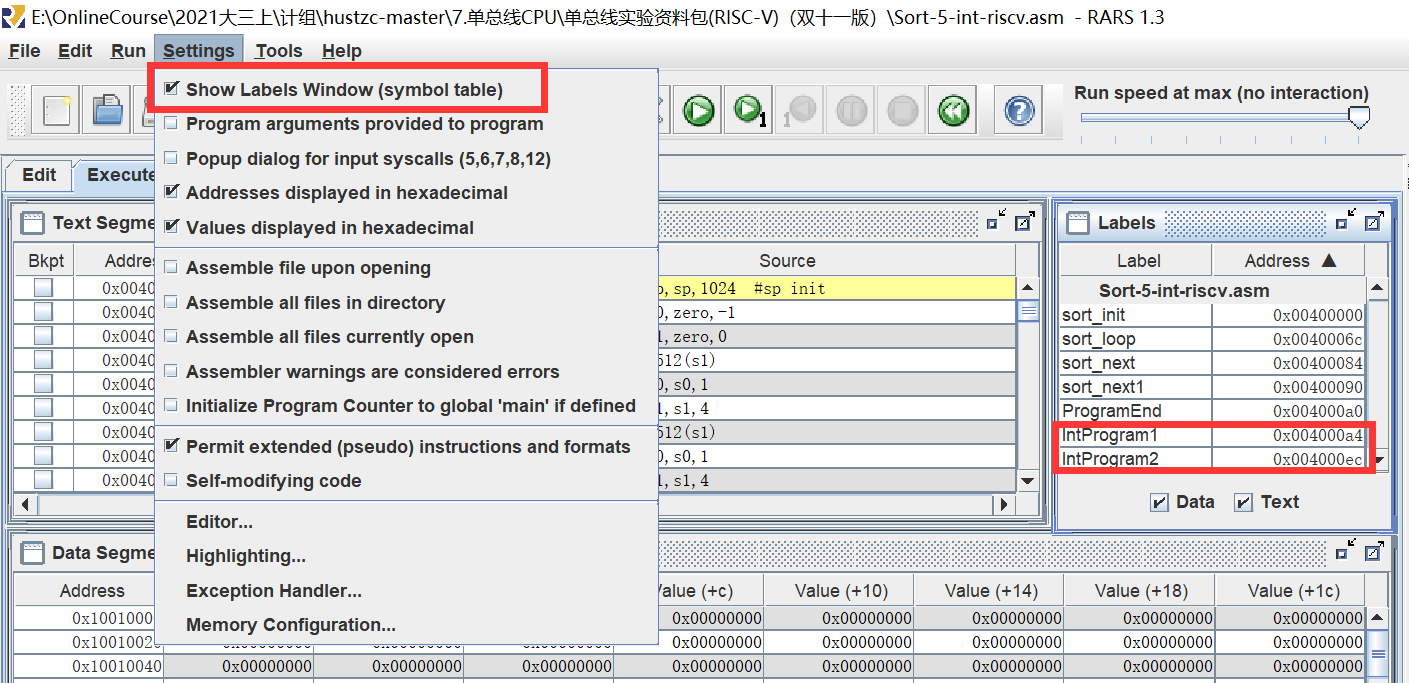

中断入口地址查看

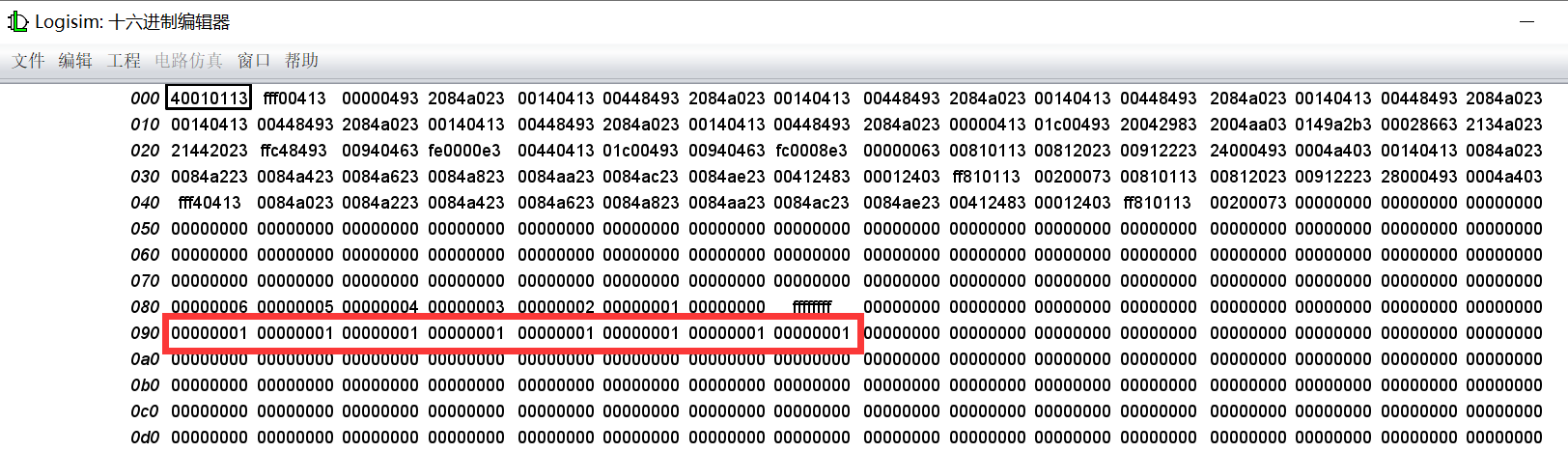

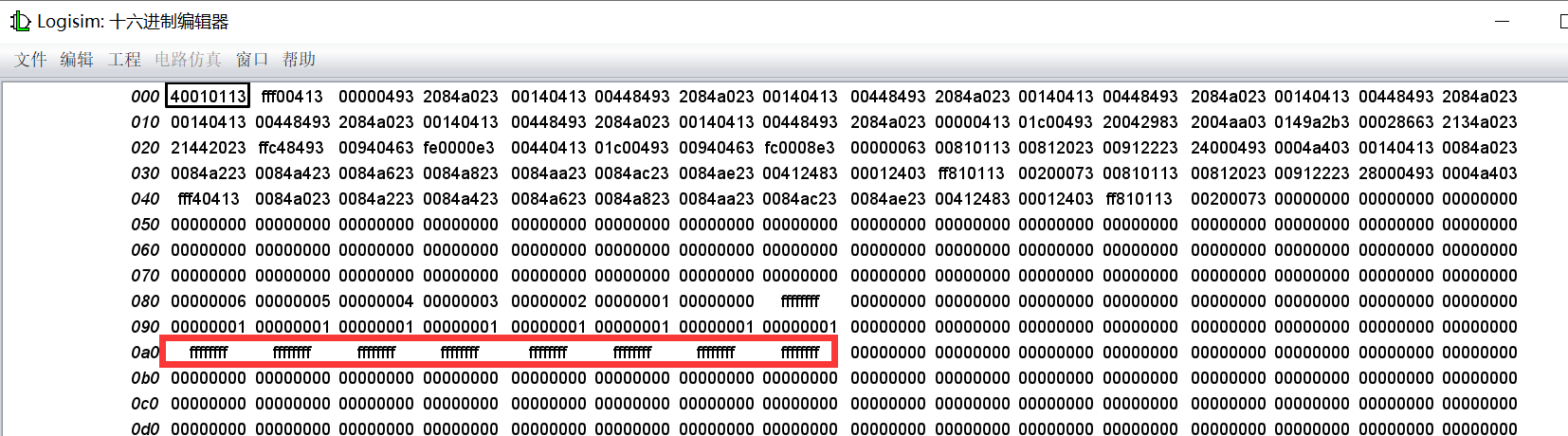

sort-5-int-riscv.hex 程序被加载到 RAM 中,并在执行后停止在指令计数 252 处。

单击 1 按钮并观察 RAM 内容。 您可以看到程序将从 90 开始的所有 8 个字单元加 1。

单击 2 按钮并观察 RAM 内容。 您可以看到程序将从 a0 开始的所有 8 个字单元递减 1。

6. 支持中断的现代顺序硬连线控制器状态机设计

只需根据这张图片填写表格即可。

(我每天填写测试集的表格)

7. 具有中断支持的现代顺序硬连线控制器设计

仍然连接。

至此所有实验已经完成,恭喜你通过了(lei)级(si)!