计算机组成原理——寄存器

文章目录

1. 寄存器

2. 带寄存器的加法器

3. 时钟信号与计算速度

1. 寄存器

上一篇D触发器可以在时钟上沿存储1位数据。如果想存储多个位(bit)的数据,就需要用多个D触发器并联实现,这种电路称之为寄存器。

寄存器是计算机中央处理器(CPU)内部的一种高速存储单元,用于临时存储数据和指令。寄存器是计算机中速度最快的存储器,直接与CPU的运算单元(如ALU)相连。

寄存器的主要功能是临时存储处理过程中需要的数据、指令地址和计算结果。寄存器的读写速度非常快,是计算机执行效率的重要保障。

-

数据寄存器(Data Register):

- 功能:用于存储数据和中间计算结果。

- 示例:通用寄存器(如x86架构中的EAX、EBX等)。

-

地址寄存器(Address Register):

- 功能:用于存储内存地址,以便访问内存中的数据。

- 示例:基址寄存器(Base Register)、变址寄存器(Index Register)。

-

指令寄存器(Instruction Register, IR):

- 功能:用于存储当前正在执行的指令。

- 示例:CPU从内存中读取指令,并将其存储在指令寄存器中进行译码和执行。

-

程序计数器(Program Counter, PC):

- 功能:用于存储下一条将要执行的指令地址。

- 示例:指向内存中的指令地址,每执行一条指令后自动加1,指向下一条指令。

-

状态寄存器(Status Register):

- 功能:用于存储CPU当前的状态和条件码(如零标志、进位标志等)。

- 示例:在算术运算后,状态寄存器中的标志位可以反映运算结果的性质(如结果是否为零)。

-

堆栈指针寄存器(Stack Pointer, SP):

- 功能:用于指示栈顶位置,管理函数调用和返回。

- 示例:在函数调用过程中,堆栈指针寄存器用于保存返回地址和局部变量。

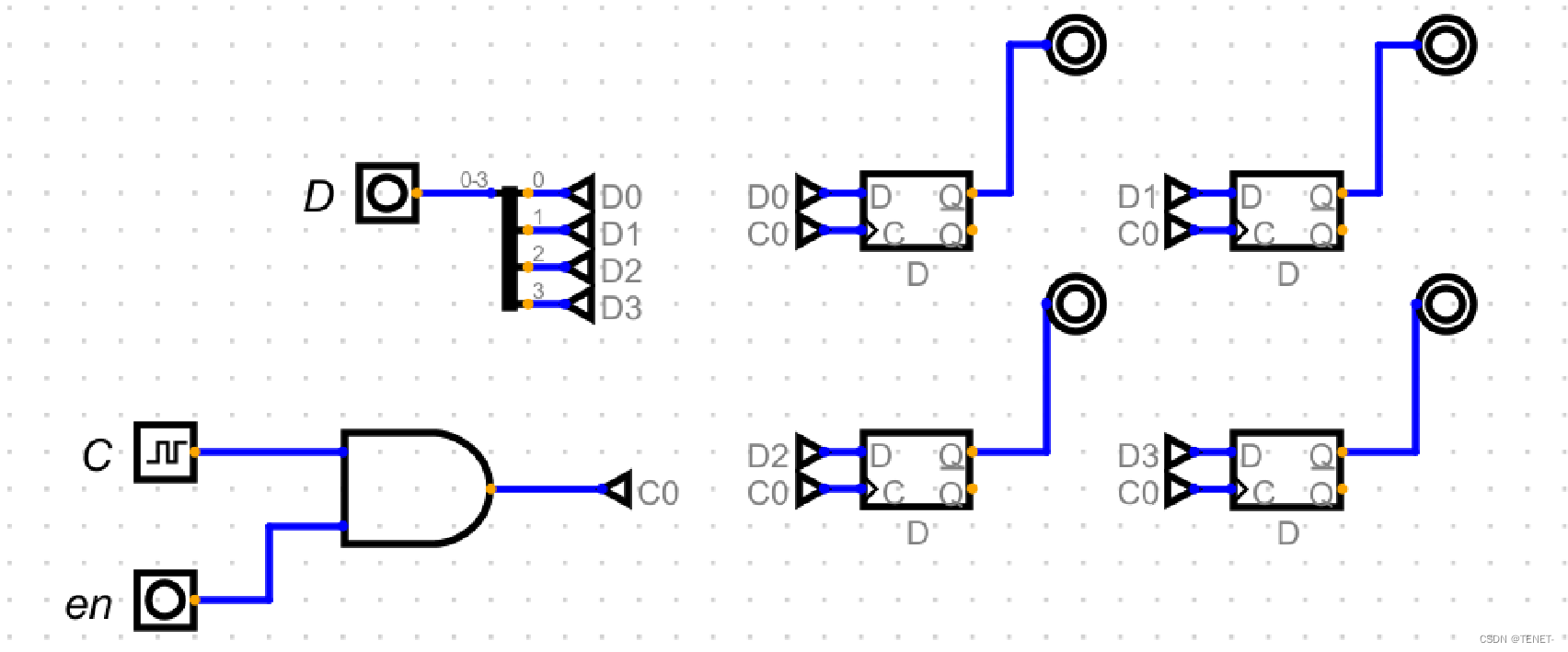

以4位寄存器为例,下面是电路图:

- 时钟信号clock:控制所有D触发器的输入数据在时钟上沿时被锁存。

- 数据输入D:4位数据输入信号(D0, D1, D2, D3)。

- 输出信号Q:4位数据输出信号(Q0, Q1, Q2, Q3)。

- 使能信号en:控制寄存器的使能状态,决定是否允许数据写入。

使能信号en = 1:

1. 时钟上沿到来时:

- 所有D触发器同时读取其对应的输入数据位,并将这些数据位存储到其内部。

- 每个D触发器的输入数据位(D0, D1, D2, D3)在时钟上沿被锁存,并输出到对应的Q端(Q0, Q1, Q2, Q3)。

2. 时钟下沿或无时钟信号时:

- D触发器保持其输出状态不变,即输出信号Q保持锁存的数据位。

使能信号en = 0:

- 当使能信号为低电平时,时钟信号对D触发器不起作用。

- 无论时钟信号如何变化,D触发器保持其输出状态不变,输出Q保持之前的值。

2. 带寄存器的加法器

带寄存器的加法器,使用了寄存器来实现加法功能。通过寄存器存储上一次计算的结果,可以避免每次使用多个加法器进行累加。

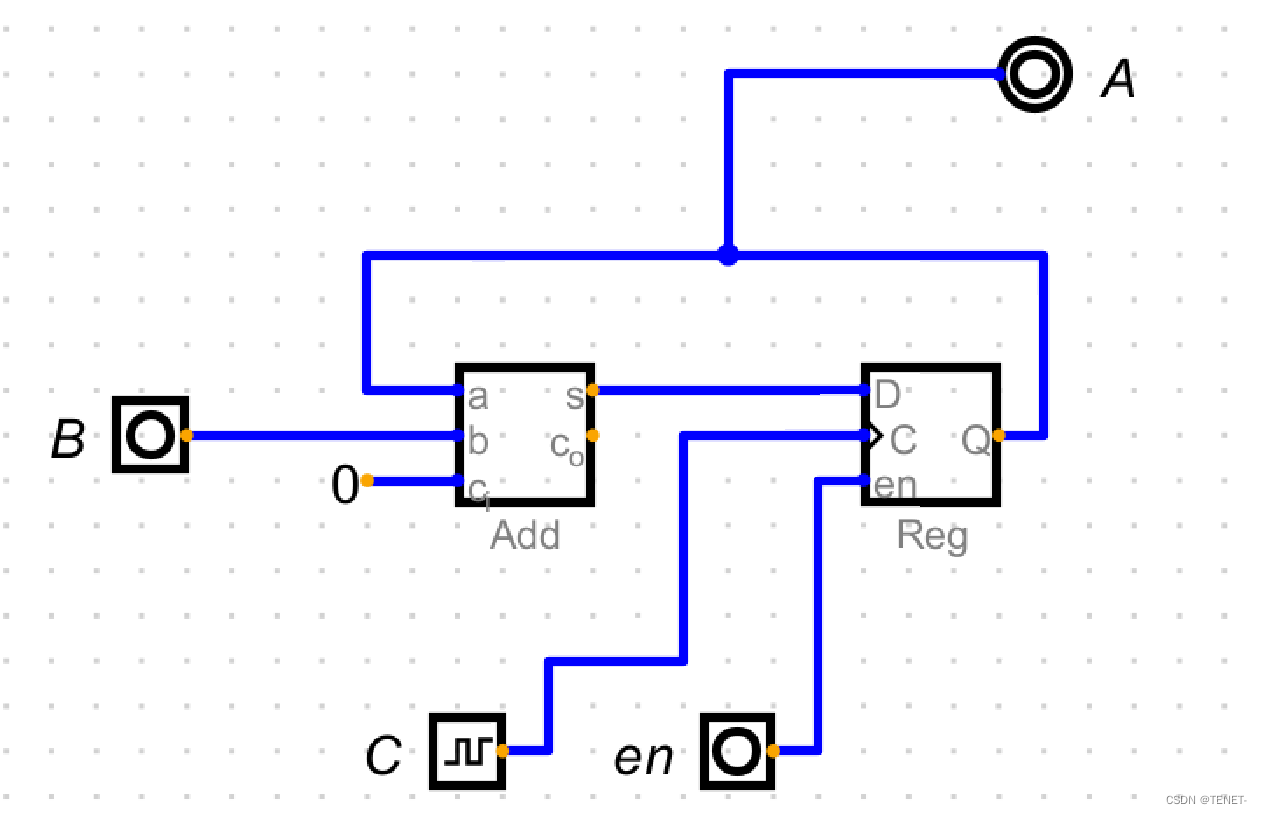

电路图展示了一个带寄存器的加法器结构,包括以下主要部分:

- 加法器(Add):执行两个输入信号的加法运算。

- 寄存器(Reg):存储加法器的输出结果。

- 使能信号(en):控制寄存器是否更新其存储的值。

- 时钟信号(C):控制寄存器在时钟上沿时更新存储的值。

工作原理

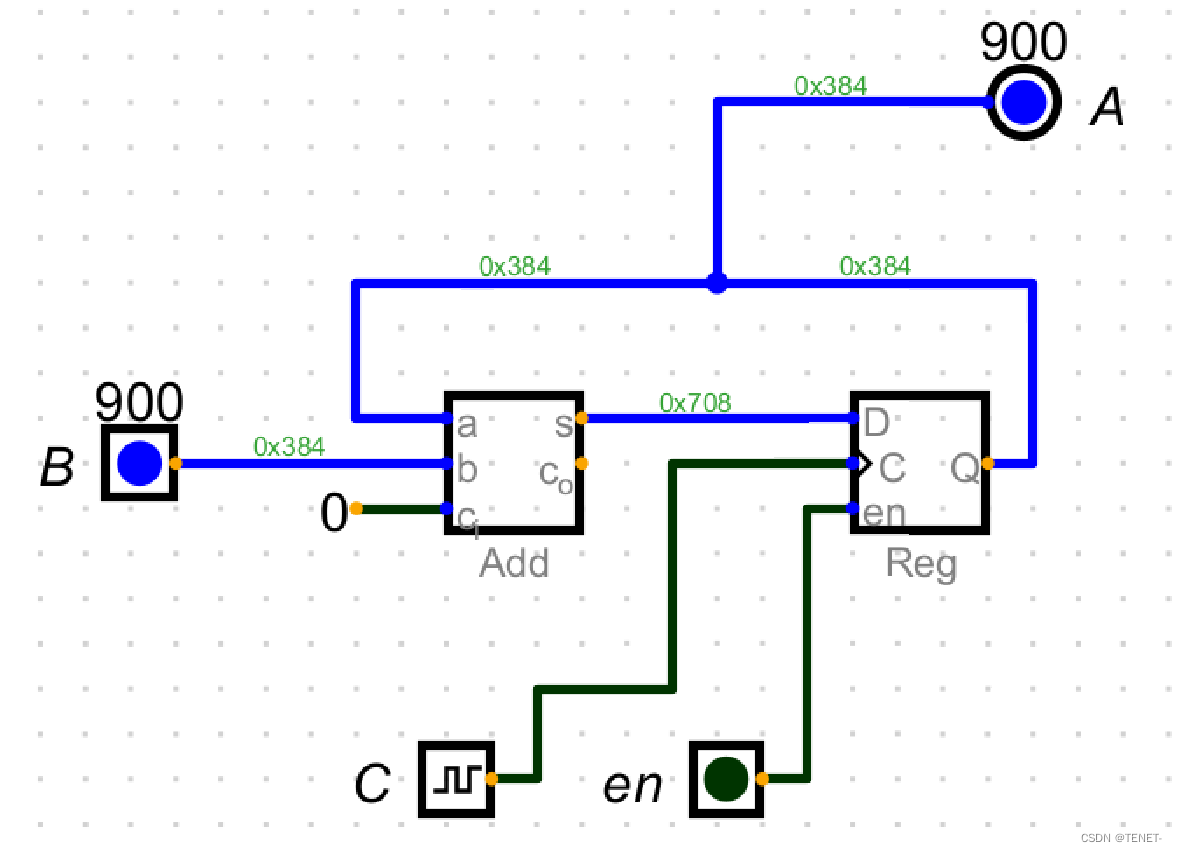

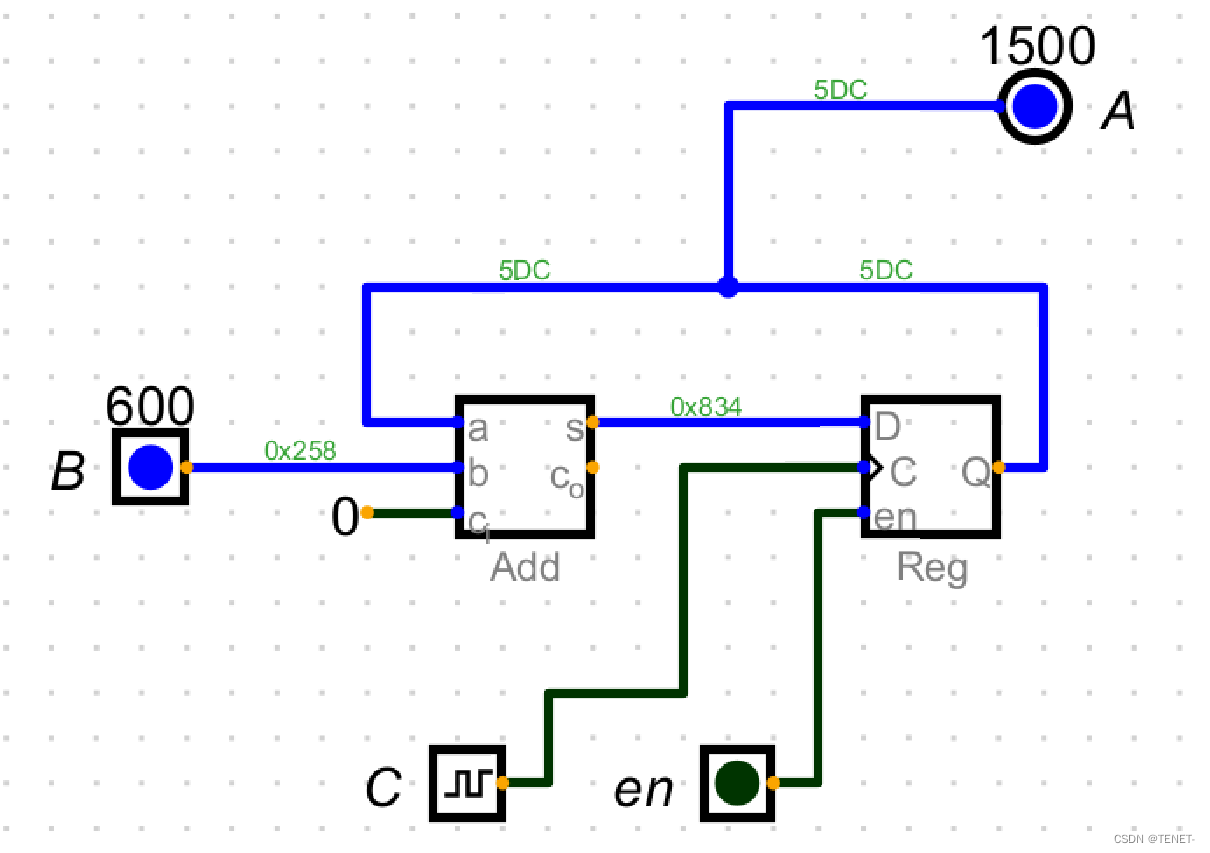

输入信号:

- B:输入数据信号,值为600(0x258)。

- A:寄存器输出的存储值,初始值为900(0x384)。

加法运算:

- 加法器执行输入信号B与寄存器输出A的加法运算。

- 结果:600 + 900 = 1450(0x5DC)。

寄存器存储:

- 使能信号en和时钟信号C控制寄存器的更新。

- 当使能信号en为高电平且时钟信号C上沿到来时,寄存器将存储加法器的输出结果(1500)。

通过使用寄存器存储上一次计算结果,可以减少对多个加法器的需求,提高电路的效率和灵活性。同时,寄存器可以在时钟信号控制下有序地存储和更新数据,确保数据处理的准确性和可靠性。

3. 时钟信号与计算速度

这里时钟信号的速度就和计算机运算的速度类似,时钟信号在数字电路中起着至关重要的作用,它提供了一个同步脉冲,使得电路中的各个部分能够在同一时间点执行操作。在带有寄存器的计算电路中,时钟信号控制着数据的存储和计算过程,决定了电路的运行速度。

计算速度与时钟频率

- 时钟频率(Clock Frequency):时钟信号每秒钟振荡的次数,以赫兹(Hz)为单位。时钟频率越高,每秒钟执行的计算周期就越多。

- 计算速度:计算器或计算机执行指令的速度,直接受时钟频率的影响。时钟频率越高,计算速度越快。

分析

电脑CPU运行速度:现代计算机的CPU运行速度通常以吉赫兹(GHz)为单位。比如一个运行速度为3.57GHz的CPU,相当于每秒钟进行35.7亿次时钟周期(35.7亿赫兹)。

- 3.57GHz = 3.57 × 10^9 Hz = 35.7亿次每秒。

自动组件时钟频率

在自动组件(如加法器、寄存器等)中,时钟频率同样决定了其工作速度:

- 高时钟频率:意味着每秒钟可以执行更多的操作周期,因此计算速度更快。

- 低时钟频率:则每秒钟执行的操作周期较少,计算速度较慢。

- 3.57GHz = 3.57 × 10^9 Hz = 35.7亿次每秒。

- D触发器保持其输出状态不变,即输出信号Q保持锁存的数据位。