AURIX TC3XX系列之GTM CMU模块

1、CMU简介

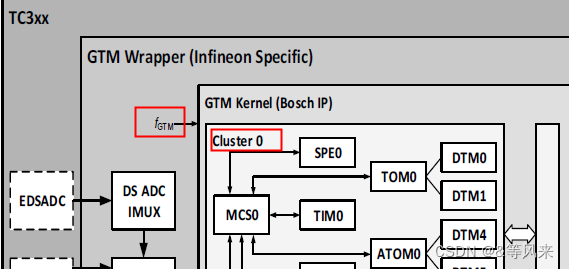

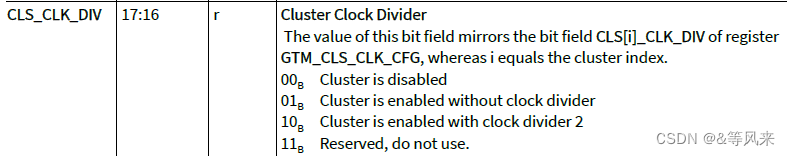

时钟管理单元(CMU)负责计数器和GTM的时钟生成。它由为整个GTM产生不同的时钟源的三个子单元组成。三个子单元分别为:CFGU(Configurable Clock Generation),EGU(External Clock Generation),FXU(Fixed Clock Generation)。CMU时钟源是Cluster 0时钟信号fcls0_clk,它由寄存器GTM_CLS_CLK_CFG中的位字段CLS0_CLK_DIV的值来定义。fcls0_clk = fGTM / CLS0_CLK_DIV

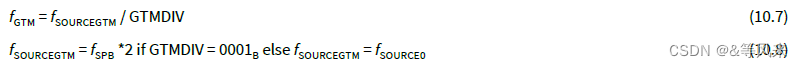

对于fGTM,它由以下公式决定

对于fSOURCE0可以参考我之前写的《AURIX TC3XX系列之时钟系统》http://t.csdnimg.cn/0Invk

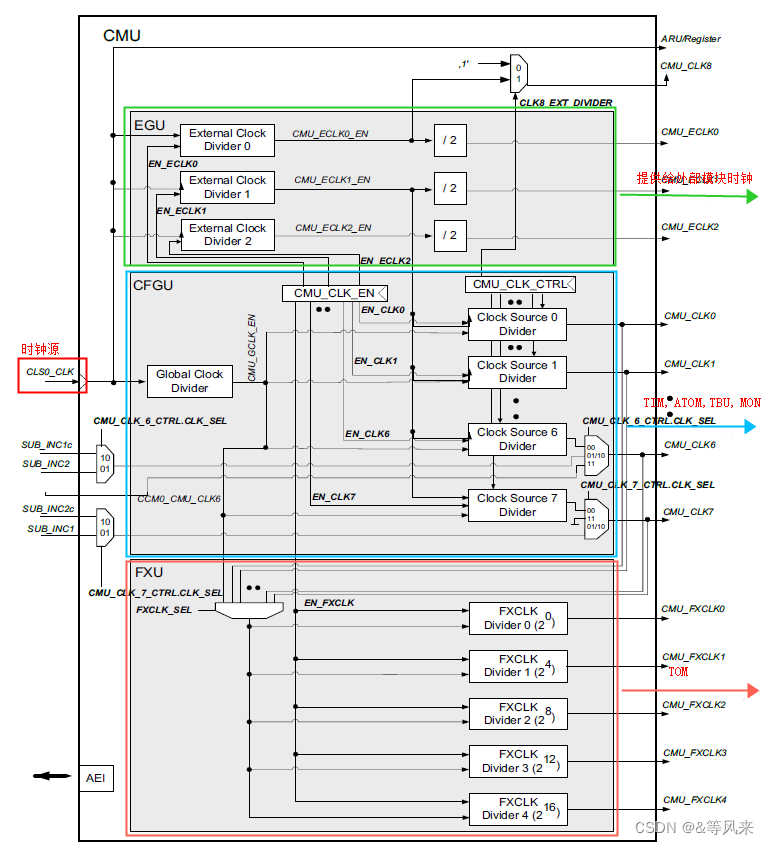

CMU结构图如下所示

2、功能介绍

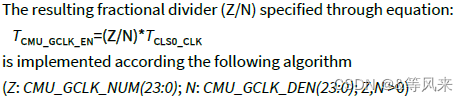

2.1 全局时钟分配器Global Clock Dvider

子块全局时钟划分器可用于将CMU主源信号CLS0_CLK划分为公共的细分时钟信号。

子块全局时钟分割器的分割时钟信号被实现为使能信号,使来自CLS0_CLK信号的专用时钟产生用户指定的分割时钟频率。

2.2 可配置的时钟生成子单元CFGU

CFGU为TIM, ATOM, TBU, MON模块提供8个独立的时钟源,每个模块都可以选择任意的时钟源。其中生成的四个时钟:CMU_CLK0, CMU_CLK1, CMU_CLK6 and CMU_CLK7用于TIM滤波器计数器。通过在寄存器CMU_CLK_EN中设置适当的位字段EN_CLK[x],可以单独启用每个时钟信号CMU_CLK[x]。

2.3 固定时钟生成子单元FXU

FXU为TOM模块提供预定义好的时钟CMU_FXCLK[y] (y: 0…4),分别对应CMU_FXCLK/2^0,CMU_FXCLK/2^4, CMU_FXCLK/2^8, CMU_FXCLK/2^12,CMU_FXCLK/2^16

。FXU的时钟输入源是全局时钟以及CFGU产生的CMU_CLK0-7。

2.4 外部时钟生成子单元EGU

EGU子单元能够产生多达三个在CMU_ECLK[z] (z:0……2)处可见的芯片外部时钟信号,其占空比约为50%。且EGU能够为模块CCM生成时钟CMU_CLK8,以管理2个时钟域。

3、MCAL配置

CMU的时钟配置基本在MCU下

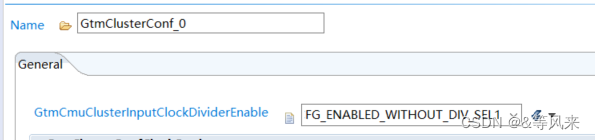

Cluster0输入时钟设置:设置不分频,即fcls0_clk = fGTM

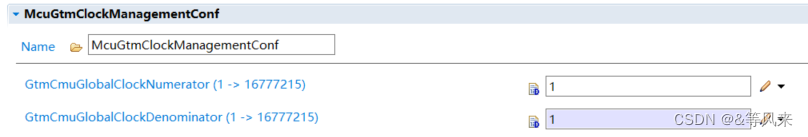

全局时钟分频设置:设置CFGU模块的时钟等于时钟源fcls0_clk

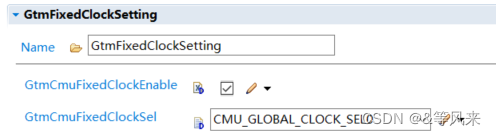

FXU设置:设置固定时钟使能,时钟选择全局时钟,即经过全局时钟分频的时钟GLOAB CLOCK

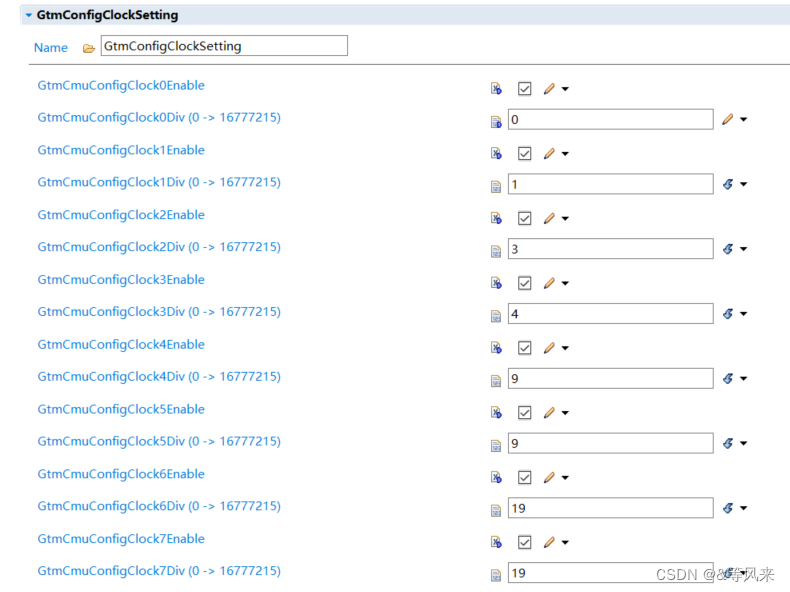

CFGU设置:设置CFGU生成的时钟使能及分频

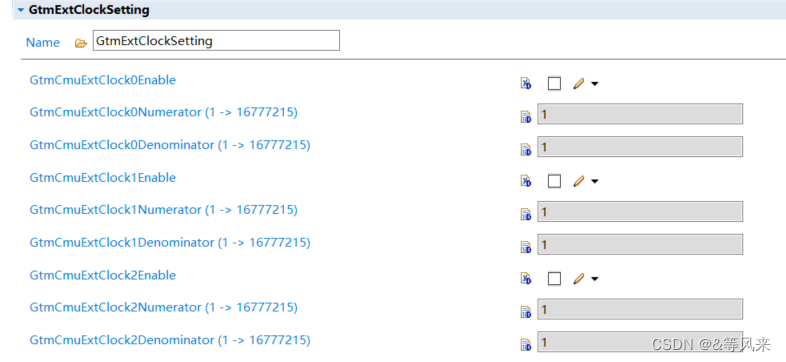

EGU设置:外部时钟使能及分频设置