【FPGA图像处理】——DDR仲裁、多输入源拼接、旋转任意角度、突发长度修改、任意地址读取。

温馨提示:这篇文章已超过389天没有更新,请注意相关的内容是否还可用!

前言:做FPGA大赛期间遇到的问题,自己coding过程。

包含:hdmi、摄像头等多输入源的拼接;了解DDR以及多种DMA传输方式,修改底层突发长度以及存储位宽;单输入源任意角度旋转(无需降低帧率)。

文章目录

- 前言

- 免责声明

- 一、hdmi、摄像头等多输入源的拼接

- 二、WDMA传输

- 三、单输入源的任意旋转

- 任意突发长度修改

- 旋转部分

- 其他事项记录

- 总结

前言

写这篇文章的原因呢,是因为之前参加FPGA大赛的时候遇到很多问题找不到系统的解决办法,本文主要提供一个大概的关于图像的大概处理流程;当然根本原因是没晋级决赛了哇,但是不得不承认我在这个比赛的过程中学习到了非常多的东西,记录下来帮助更多希望入门FPGA和图像处理的朋友们。接下来的内容会以提出问题->分析问题->解决问题的形式展示。

免责声明

本人做FPGA很多年,但是系统的做FPGA图像处理这是第一次,本文仅记录一月以来的调试内容,如果内容有问题请通过邮箱联系我,评论偶尔会看。代码(紫光同创版)免费提供(仅仅提供我写的部分)

一、hdmi、摄像头等多输入源的拼接

问题:DDR在某个时刻只能进行读或者写操作的条件下如何进行数据处理?怎么才能最大程度的减缓帧丢失?

在使用xilinx系列FPGA的时候里面有一个很常用的IP:AXI-interconnect;AXI-interconnect是一个一主多从的模块,对多通道从机进行数据缓存通过自动仲裁,输出。他的优点简单,emm,只有简单。

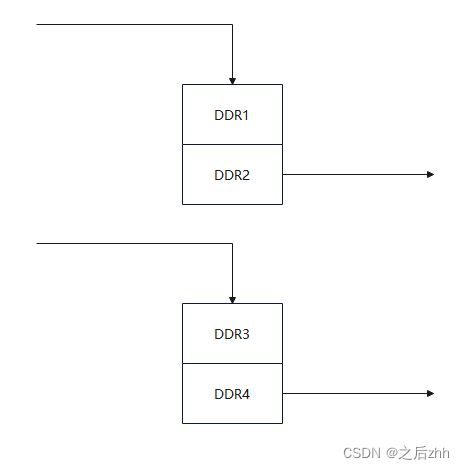

最初,解决这个问题的时候进行了降帧的处理,即DDR的某片区域存够了摄像头或者hdmi输入的一帧数据进行暂停处理,当DDR的另一片区域也存够了hdmi或者摄像头输入的一帧再进行输出。

如图所示,每个区域会在存满一帧以后等待另一个输入也存满的时候进行输出,然后在此进行下一次存储。这样造成的结果会使得两个输入源的帧率成倍的降低。

那么我们在没有AXI-interconnect IP的条件下,如何进行仲裁呢?怎么才能减缓帧率的丢失呢?

为了解决这个问题,我使用的数据仲裁方法是——固定优先级算法进行仲裁。

if(wfifo_rcount_1 >= wr_bust_len )begin state_cnt = wr_bust_len )begin state_cnt datain,16'd0}), // input [31:0] .wr_full (), // output .wr_water_level(), // output [12:0] .almost_full (), // output .rd_clk (ddr_clk), // input .rd_rst (!rst_n|wfifo_rst_h), // input .rd_en (wfifo_rden), // input .rd_data (wfifo_dout), // output [255:0] .rd_empty (), // output .rd_water_level(wfifo_rcount), // output [9:0] .almost_empty () // output );